基于ARM+FPGA+多DSP的嵌入式实时图像处理系统

实时图像处理、高速数据运算处理要求其系统具有对数据处理速度快、数据吞吐率高以及多任务处理功能。目前大多数方案都是采用HPI数据传输方式,将ARM和DSP进行组合完成一些图像处理,DSP处理器只是完成图像采集、压缩、编码等简单的处理[1]工作,不能满足实时的智能识别或大数据量运算的视频处理要求。在应用领域方面也会因其处理速度问题受到一定的限制。

例如,胎儿性别屏蔽项目中,要对实时视频进行性别部位的检测和屏蔽,若采用单DSP则会出现漏帧或视频不流畅;应用于高速运动物体跟踪时,单DSP无法实现实时运动物体跟踪,例如汉王科技的运动检测和海康威视运动检测,都不能实时检测,即使检测也会出现漏检现象和视频不流畅。当处理4CIF或者更大图像时,单DSP的处理能力又会下降,虽然可以将图像缩小进行处理,但是缩小图像则会丢失一些重要的图像信息,使得智能识别准确率下降。

针对上述情况,设计一种能够实现进行快速信号处理和数据交换的实时图像处理系统很有必要。

1 系统结构

1.1 结构

系统功能:利用S3C6410进行数据整合、任务调度、人机交互;利用TMS320C6416进行算法运算;每个DSP与FPGA都是无缝连接。设计中利用FPGA实现的FIFO进行与DSP之间的高速数据传输以及ARM对多个DSP的任务调度处理等。

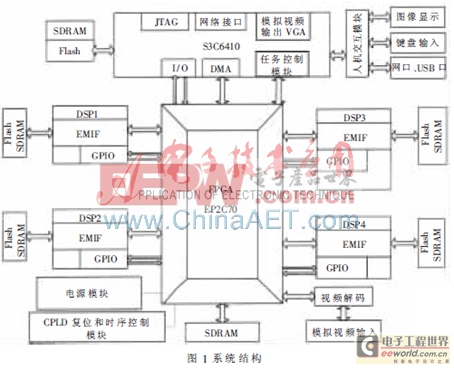

系统结构如图1所示。系统由1个ARM11处理器S3C6410(主处理器)与4个TMS320C6416(720 Hz)(从DSP)通过FPGA(EP2C70~7)实现互联的ARM+多DSP的嵌入式图像处理系统。所有的DSP都通过外部存储器接口(EMIF)与FPGA无缝相连,每个DSP之间的数据传输是通过FPGA内部互联FIFO网络实现。

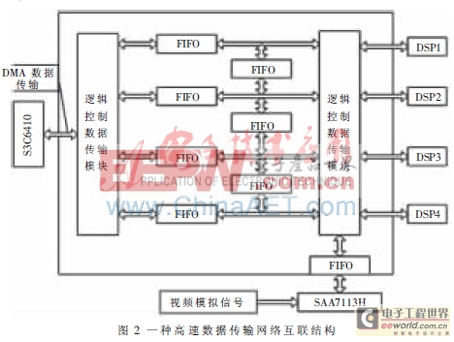

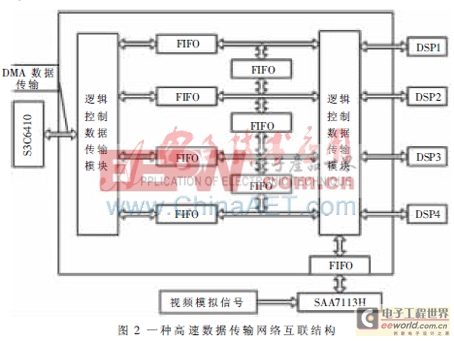

图2所示是一种互联的FIFO网络结构和高速数据传输网络结构。主处理器通过DMA数据访问模式与FPGA的双口FIFO连接,从而实现与FPGA通过FIFO连接的所有从DSP进行通信,所有FIFO都是双向的,FIFO及其读写控制逻辑都在FPGA内部实现。

FPGA中的FIFO读写状态控制、各从DSP之间通信的同步握手信号、S3C6410处理器数据请求等逻辑信号,都是由每个DSP的一部分GPIO口与EP2C70的I/O口连接实现。

1.2 特点

系统结构具有可重构特性,在硬件平台不变情况下,只需通过改变FPGA程序代码就可以完全改变系统结构,以适应不同的算法结构。如图2中屏蔽DSP1~DSP4之间的互相通信,即可组成主从并行的流水线结构;若需要串行的流水线结构,只需将DSP1~DSP4的其中一个与S3C6410通信即可;若需要设计更复杂的串并混合性结构,也只需改变FPGA的代码就能够很容易地实现。

2 S3C6410的DMA与FPGA的软FIFO

接口实现

2.1 S3C6410简介

S3C6410是三星公司的产品采用ARM1176JZF-S核,包含16 KB的指令数据Cache和16 KB的指令数TCM;ARM Core电压为1.1 V时,可以在553 MHz下运行。在1.2 V时,可以在667 MHz下运行。通过AXI、AHB和APB组成的64/32 bit内部总线与外部模块相连。SROM Controller:6个片选,支持SRAM、ROM和NOR Flash以及支持8/16 bit,每个片选支持128 MB。JPEG Codec:支持JPEG编解码功能,最大尺寸为4 096×4 096。2D GRAPHICS:2D加速,支持画点/线,bitblt功能和Color Expansion。3D GRAPHICS:3D加速。

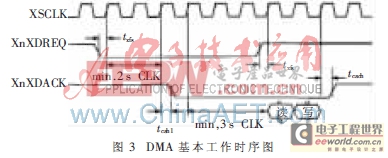

S3C6410可支持4个DMA控制器,用于系统总线内部或与外围总线之间的数据交换,每个控制器包含8个通道,支持8/16/32 bit传输。现以外部DMA请求为例简要介绍DMA的工作过程。图3所示为DMA基本工作时序。

当需要进行DMA操作时,外部DMA请求引脚XnXDREQ置为低电平。此时DMA控制器向CPU发出占用总线的请求,当总线请求成功后,XnXDACK引脚变为低电平,表示CPU已经将总线使用权交给DMA控制器,可以进行数据传输。当数据传输完成后,应答信号XnXDACK置为高电平,通知CPU完成一次DMA操作。

S3C6410提供了三种不同的DMA操作模式:单服务命令模式、单服务握手模式和全服务握手模式。在利用DMA进行数据传输前必须对其相关寄存器进行设置,包括源地址寄存器、目的地址寄存器和各自的控制寄存器以及配置DMA模式的控制寄存器等。

2.2 FPGA及其实现FIFO[2]

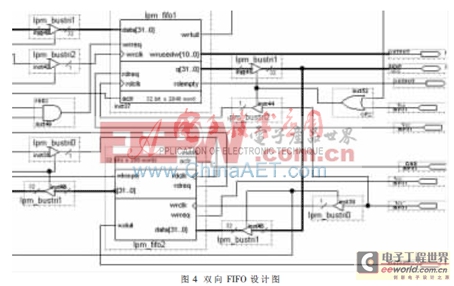

采用FPGA 实现多时钟电路系统时,需要处理不同的时钟域之间速率匹配问题,可利用FPGA内部生成的异步FIFO来处理。异步FIFO主要由双端口RAM、写地址产生模块、读地址产生模块、满空标志产生模块组成。双端口RAM由FPGA的Block RAM块构成,FPGA采用Atera公司的EP2C70-896C7,其Block RAM读写时钟频率可以达到216.73 MHz,因此选用Block RAM作为存储体,不仅速度快,而且设计简单。设计时,一个端口配置成写端口,另一端口配置成读端口,然后把Block RAM 的管脚与相对应的控制信号相接即可。读写地址通过FPGA芯片内部的二进制进位逻辑产生,以对应Read_En/Write_En作为使能信号在读/写时钟的控制下进行计数。空或满标志可以由读或写地址的相对位置来获得。本系统采用2个FIFO组成一路数据传输通道,双向FIFO的设计图如图4所示。

2.3 S3C6410的DMA与软FIFO接口实现

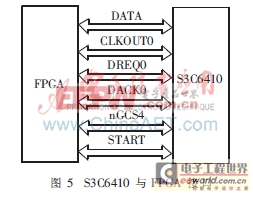

根据DMA接口原理,设计S3C6410与FPGA之间的接口简图如图5所示。

读时钟由ARM的时钟输出引脚CLKOUT0提供。CLKOUT0根据S3C6410内部寄存器的设置可以输出不同的时钟频率。FIFO输出数据经过以nGCS4为选通信号的缓冲器(Buffer)后接到S3C6410的数据总线上。nGCS4是S3C6410存储空间中BNAK4的片选信号,当S3C6410对该信号对应存储空间进行读写操作时,BANK4为低电平,其余时间均为高电平。

FIFO的写请求信号由S3C6410与FIFO的满状态共同控制。当S3C6410发出START信号并且FIFO未满时,写请求信号为高电平,FIFO在写时钟的控制下写入数据;当START信号撤销或者FIFO满时,写请求信号变为低电平,停止写操作。

FIFO的读操作与S3C6410的DMA操作配合进行。系统采用单服务命令模式的DMA操作,每次传输一个字节的数据。当DREQ0信号变为低电平时,DMA操作开始,每次传输一个字节后产生一个DACK0应答信号,而且只要DREQ0为低电平DMA操作就继续进行,直到DMA控制寄存器中的计数器为0,产生DMA中断。根据上述时序特点,将FIFO的空信号作为DMA的请求信号DREQ0。当CCD输出的数据写入FIFO中时,空信号跳变为低电平启动DMA操作,同时以DACK0信号作为FIFO的读请求。每次DMA传输完成后应答信号使FIFO的读指针移动一位,以实现数据的快速准确采集。

3 图像采集模块

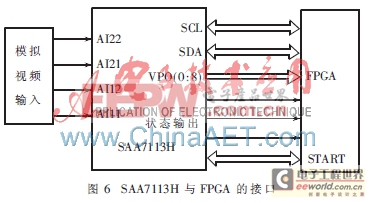

用可编程视频输入处理器SAA7113H进行视频信号处理。SAA7113H内部集成了强大图像色度、亮度处理功能以及多种输出模式[3];有32个工作寄存器,在系统复位时,必须通过I2C总线对其进行初始化。本系统使用灰度图像,没有使用色度信号,所以数据线为8 bit。SAA7113H与FPGA的接口如图6所示。

评论