基于AT89C52单片机的日历时钟模块设计

在实时监控系统的设计中,要实时监测各个控制信号,更重要的是在发生故障时能准确记录故障数据,以便准确分析排除错误。监控系统中一般都要定时采集现场数据,对某些重要的信息不仅要记录其内容,还要记录下该信息发生的准确时间,所记录的实时时间信息应长期保存,因此需要实时时钟来实现。常用的单片机没有实时时钟,若需采用定时器实现,一旦系统掉电,时钟就不能运行,这是实时监控系统

不允许的,而采用独立运行的实时时钟便可实现。但一般的时钟芯片在系统掉电时,其数据也会丢失,需提供备用电池。而时钟芯片DS12887在系统掉电时数据不丢失,广泛应用于测量和控制系统。因此,这里给出了实时时钟DS12887在单片机应用系统中的应用。

1 主要器件造型

1.1 DS12887的功能介绍

DS12887是DALLAS公司推出的8位并行并自带RAM的实时日历时钟芯片,内部有14个时钟控制寄存器,包括10个时标寄存器,4个状态寄存器和114 bit作掉电保护用的低功耗RAM。CPU通过读DS12887的内部时标寄存器得到当前的时间和日历,也可通过选择二进制或BCD码初始化芯

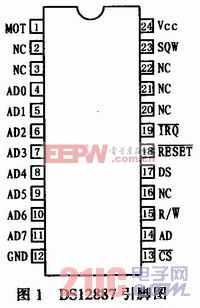

片的10个时标寄存器,其4个状态寄存器用来控制和指出DS12887的当前工作状态,114 bit非易失性静态RAM可在掉电时保存一些重要数据。 DS12887功能强大,应用广泛。其引脚功能如下:

GND,VCC:直流电源+5 V电压。当5 V电压在正常范围内时,数据可读写;当VCC低于4.25 V,读写禁止,计时功能仍继续;当VCC下降到3 V以下时,RAM和计时器被切换到内部锂电池。

MOT(模式选择):MOT引脚接到VCC时,选择MOTOROLA时序,当接到GFND时,选择INTEL时序。

SQW(方波信号):SQW引脚能从实时时钟内部15级分频器的13个抽头中选择一个作为输出信号,其输出频率可通过对寄存器A编程改变。

AD0~AD7(双向地址/数据复用线):总线接口,可与MOTOROLA微机系列和INTEL微机系列接口。

AS(地址选通输入):用于实现信号分离,在AD/ALE的下降沿把地址锁入DS12887。

DS(数据选通或读输入):DS/RD有2种操作模式,取决于MOT引脚的电平,当使用MOTOROLA时序时,DS是一正脉冲,出现在总线周期的后段,称为数据选通;在读周期,DS指示DS12887驱动双向总的时刻;在写周期,DS的后沿使DS12887锁存写数据。选择INTEL时序时,DS称作(RD),RD与典型存储器的允许信号(OE)的定义相同。

![]() (读/写输入):也有两种操作模式。选MOTOROLA时 序时,

(读/写输入):也有两种操作模式。选MOTOROLA时 序时,![]() 是一电平信号,指示当前周期是读或写周期,DSO为高电平时,

是一电平信号,指示当前周期是读或写周期,DSO为高电平时,![]() 高电平指示读周期,

高电平指示读周期,![]() 低电平指示写周期;选INTEL时序,

低电平指示写周期;选INTEL时序,![]() 信号是一低电平信号,称为WR。在此模式下,R/W与通用RAM的写允许信号(WE)的含义相同。

信号是一低电平信号,称为WR。在此模式下,R/W与通用RAM的写允许信号(WE)的含义相同。

![]() (片选输入):在访问DS12887的总线周期内,片选信号必须保持为低。

(片选输入):在访问DS12887的总线周期内,片选信号必须保持为低。

![]() (中断申请输入):低电平有效,可作微处理的中断输入。没有中断条件满足时,IRQ处于高阻态。IRQ线是漏极开路输入,要求外接上接电阻。

(中断申请输入):低电平有效,可作微处理的中断输入。没有中断条件满足时,IRQ处于高阻态。IRQ线是漏极开路输入,要求外接上接电阻。

![]() (复位输出):当保持低电平时间大于200 ms,保证DS12887有效复位。

(复位输出):当保持低电平时间大于200 ms,保证DS12887有效复位。

DS12887引脚如图1所示。

DS12887的内部地址分配:地址00H和03H单元取值范围是00H~3BH(十进制为0~59);04H~05H单元按12小时制取值范围是上午(AM)01H~0CH(十进制为1~12),下午(PM)51H~5CH(十进制为81~92),按24小时制取值范围是00H~17H(十进制为0~23);06H单元的取值范围是01H~07H(十进制为1~7);07H单元取值范围O1H~1FH(十进制为1~31);08H单元取值范围是01H~0CH(十进制为1~12);09H单元取值范围是00H~63H(十进制为0~99)。

1.2 单片机A789C52简介

AT89C52是一个低功耗,高性能CMOS 8位单片机,片内含8 kB的可反复擦写的Flash只读程序存储器和256字节的随机存取数据存储器(R-AM)。该器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器和Flash存储单元。A-T89C52有40个引脚,32个外部双向输入/输出(I/O)端口,内含2个外中断口,3个16位可编程定时计数器,2个全双工串行通信口,其将通用的微处理器和Flash存储器结合在一起,特别是可反复擦写的Flash存储器可有效降低开发成本。广泛应用于智能仪器、仪表和低功耗电子产品。

2 系统硬件设计

2.1 DS12887的工作原理

DS12887采用8位地址/数据复用的总线方式,具有一个锁存引脚,通过读、写、锁存信号实现其内部数据的输入输出,控制内部的控制寄存器、读取内部的时间信息寄存器。DS12887的各种寄存器在其内部空间都有相应的固定地址,因此,单片机通过正确的寻址和寄存器操作就可以获取需要的时间信息。DS12887有2种工作时序,即Motorola和Intel时序,由Mot引脚的电平指定。当MOT引脚为高电平时选择Motorola时序;为低电平时选择Intel时序。除此之外DS12887内部还有128字节的RAM的单元,其中前10个字节用于存放日历时钟信息,字节0为秒,字节2为分,字节4为时,字节6为星期,字节7为日,字节8为月,字节9为年,字节0AH~0DH用作控制和状态寄存器,剩下的114字节为用户RA-M,所有的这128字节都是掉电非易失性的。

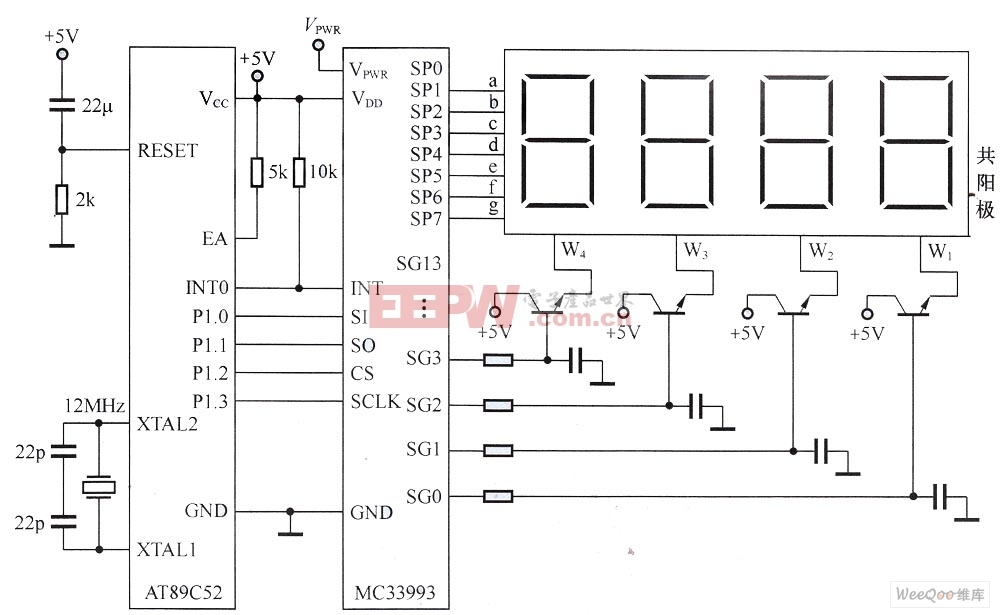

2.2 DS12887与单片机的接口设计

单片机的P0口用作地址/数据复用总线与实时时钟DS12887的AD0~AD7引脚相连。单片机的ALE引脚和DS12887的锁存输入引脚直接相连,用作地址锁存,实现数据和地址线的分时复用。DS12887的MOT引脚接地,用以选择Intel总线时序模式,在Intel总线时序模式时,和51单片机的接口完全兼容,可以将其读输入DS、写输入![]() 与单片机的相应引脚直接连接。DS12887的RESET引脚对日历时钟和RAM没有影响,但影响DS12887的命令和状态寄存器的内容。在电路中直接将RESET连至Vcc,这样可以保证DS12887在进入或退出电源失效状态时,其工作状态不受RESET引脚的影响。DS12887的可编程输出方波引脚SQW输出频率为2~256 Hz的方波,该系统则利用SQW引脚输出周期为125 ms的方波作为单片机外部中断/INT0的中断源,实现周期性中断。当中断发生时,单片机读一次输入口,检查电表是否转过一圈,整点时还要采一次三相电流和电压。

与单片机的相应引脚直接连接。DS12887的RESET引脚对日历时钟和RAM没有影响,但影响DS12887的命令和状态寄存器的内容。在电路中直接将RESET连至Vcc,这样可以保证DS12887在进入或退出电源失效状态时,其工作状态不受RESET引脚的影响。DS12887的可编程输出方波引脚SQW输出频率为2~256 Hz的方波,该系统则利用SQW引脚输出周期为125 ms的方波作为单片机外部中断/INT0的中断源,实现周期性中断。当中断发生时,单片机读一次输入口,检查电表是否转过一圈,整点时还要采一次三相电流和电压。

DS12887与单片机的硬件接口电路如图2所示。

评论