嵌入式实时系统开发的正确选择

嵌入式系统开发生命周期

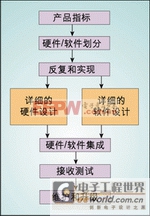

许多系统设计工程师都会经历硬件/软件协同设计的过程(图1),此过程中硬件与软件将同时进行开发。理解硬件与软件功能相互之间的关系及界限有助于确保设计要求得到完整正确的理解和实现。

早在设计要求的定义与分析阶段,系统开发人员就必须与设计工程师协同分配硬件或/和软件方面的要求。这种分配的依据是早期系统仿真、原型设计和行为建模结果、工程师自己的经验以及上文提及的各种因素权衡结果(图2)。一旦分配结束,就可以立即着手具体的设计和实现。实时系统开发中软硬件的并行设计会使用到各种分析技术,包括:

1. 硬件与软件仿真;

2. 硬件/软件协同仿真;

3. 可调度的建模技术,如速率恒定分析;

4. 原型设计和渐进式开发。

可以在各种抽象层次使用的仿真技术主要用于开展早期的性能评估。低层仿真可以用来为总线宽度和数据流程建模,这对性能评估是非常有用的。高层仿真可以满足功能的交互,并促成硬件/软件权衡研究及有效性设计。利用仿真可以将一个复杂的系统向下抽象成基础组件和行为。仿真还助于解决功能性问题(数据与算法)、行为(进程排序)或性能问题(资源利用、吞吐量和时序)。

理解设计要求

在作执行任何类型的处理器评估时,首先要详细理解用户的功能和非功能性要求。功能性要求通常比较容易获得,而非功能性要求较难定量测量。但对于实时系统来说,定义响应时间这样的要求是非常重要的。实时要求可以有以下几种:

1. 激励-激励(S-S):到系统去的两个激励之间的实时关系;

2. 激励-响应(S-R):一个激励与来自系统的一个后序响应之间的实时关系;

3. 响应-激励(R-S):一个响应与到系统去的一个后序激励之间的实时关系;

4. 响应-响应(R-R):来自系统的两个响应之间的实时关系。

S-R和R-R关系定义了对指定系统的时序要求。这种情况下所实现的功能必须足够快(或足够慢)才能满足时序要求。S-S和 R-S约束暗示系统必须能够从环境(可能是一个用户或另外一个系统)中检测出特定时序约束的破坏。这些约束与功能的快慢没有关系,相反它们能够检测出某些遭到破坏的时序约束并采取必要的措施。

因此要从最初系统要求设计时就很好地理解这一点,因为S-R和R-R约束可以引导设计工程师进行代码优化,而S-S和R-S约束需要用额外的软件来检测和响应时序冲突。

处理器选择

嵌入式实时系统比较适合用于系统优化。由于这些系统主要用来解决范围相对较窄的问题,因此硬件和软件能够得到最佳优化,并很好地应用于单一设备。这样做的目的是要在软硬件最佳折衷状态下开展系统设计。影响这一阶段设计的主要因素是处理器的选择、软硬件的分割和总体系统集成。

在为嵌入式实时系统选择处理器时需要考虑以下几个方面:

1. 性能:处理器必须有足够的性能执行任务和支持产品生命周期。

2. 实现:根据具体应用情况,处理器可能需要被高度集成。在DSP应用中可以有好几种选择,专用集成电路(ASIC)就是其中的一种。这些器件可以被用作 DSP协处理器,但对于许多通用信号处理来说显得不够灵活。另外可以选择精简指令集计算机(RISC)处理器。这些处理器的时钟速度特别快,但可扩展性不是很强,而且会发生其它实时(可预测性)问题。现场可编程阵列(FPGA)是一种快速器件,能够快速高效地完成某些DSP功能,但与DSP相比开发难度比较大,因为在DSP中一个简单的程序就能完成相同的功能。如果是主信号处理应用,则最好采用性能强大功耗也较大的通用处理器。如果需要快速升级信号处理应用,采用DSP等可编程器件比定制的硬件方案要更好些。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论