基于DSP的指纹采集系统的研究

在各种生物识别技术中,指纹识别技术是最成熟、准确和最易使用的。而指纹采集作为指纹识别系统中的一个重要环节也越来越受到人们的重视,高质量的指纹采集技术已成为一个重要的研究课题。指纹图像的采集是自动指纹识别系统(AFIS-Automation Fingerprint Identification System)的重要组成部分,采集到的指纹图像的质量好坏,直接影响到后续的指纹图像处理过程。高质量的指纹图像可以大大简化指纹图像处理的算法,提高识别率,减小拒识率。

随着新型半导体指纹采集传感器件和DSP,CPLD技术的发展,自动指纹识别技术正向着小型化和嵌入式的方向发展。本文介绍的就是基于DSP的指纹采集系统。

本系统的原理

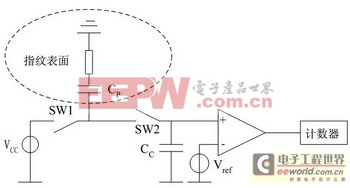

本系统中的指纹传感器采用FPS200固态指纹芯片,其成像原理如图1所示。由图1可以看出,一个像素点上有一个金属电极,手指皮肤是另一个电极,两者之间形成了电容CP。手指皮肤上的脊(ridge)和谷(valley)将产生不同的CP。由于CP很小,无法直接测量,所以使用以下方法:先以一固定时间对CP充电(SW1关且SA2开),接着以一固定时间对CP放电(SW1开且SW2关),放出的电能将转储到Cc中。每一次充电放电周期中,由于充电电压相同,充电时间相同,所以不同的CP值将导致CP存储不同的电能。这些电能在CP放电时将转储到Cc中导致Cc电压的增高。所以CP值的不同将导致一次充电放电周期结束后Cc电压增高值的不同(成正比),最后将导致Cc电压增高到参考电压所需的充电放电周期次数的不同(成反比),这样就可以通过充电放电周期次数来测量CP了。

图1 FPS200指纹成像原理

传感器阵列包括256列×300行的传感器电极,每一列都有两个采样—保持电路与之相联系。采集一个指纹图像时获取一行数据,而此过程共有两个阶段。第一阶段,传感器电极中被选择的行预充电到VDD电平,一个内部信号允许第一采样—保持电路集合保存预充电行的电平。第二阶段,行传感器电极以一定电流放电,每个单元的放电率跟“放电电流”成比例。经过一段时间(即“放电时间”)后,一个内部信号允许第二采样——保持电路集合保存最终电极的电平。预充电与放电后的电极电平之间的差别在于传感器电容量。行获取结束后,就可以对行中的每个单元进行A/D转换了。芯片的敏感度可以通过调整放电时间与放电电流来控制;电流源的参考值由外接于ISET和地之间的电阻来决定,其由放电电流寄存器(DCR)控制;放电时间由放电时间寄存器(DTR)控制。

当指纹中的凸起部分置于传感电容像素电极上时,电容会有所增加,通过检测增加的电容就能进行指纹采集。传感器中的像素点大小为45μm2,间隔为50μm,像素阵列的分辨率略高于500dpi,基于一种标准的单一多晶硅三层金属0.5μm CMOS工艺。

处于指纹的凸起下的像素(电容量高)放电较慢,而处于指纹的凹处下的像素(电容量低)放电较快。这种不同的放电率可通过采样保持(S/H)电路检测并转换成一个8位数字量输出,这种检测方法对指纹凸起和低凹具有较高的敏感性,并可形成非常好的原始指纹图像。指纹图像依次进行逐行采集,每个金属电极均作为电容的一个极,与之接触的手指则是电容的另一个极。在器件表面有一层钝化层,作为电容两个电极间的电介质层。将手指置于传感器上时,指纹上的凸起和凹进会在阵列上产生不同的电容值,并构成用于认证的一整幅图像。

系统硬件设计

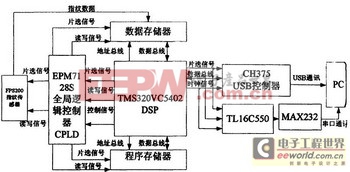

本系统的工作主要由以下部分构成:指纹图像采集部分、程序与数据存储部分、全局逻辑控制部分以及数据通信部分。

指纹图像采集部分:系统利用软件查询方式来判断是否进行指纹的采集。当进行指纹采集时,指纹传感芯片按照设定的参数采集指纹并将模拟图像转换成数字图像,然后在DSP的控制下将数据存储在外部数据空间中,等待进行下一步的处理。

图2 系统硬件原理框图

程序与数据存储部分:此部分由SRAM和DSP片内DARAM构成,SRAM用于存放指纹图像并提供程序运行时所需要的临时数据空间。

全局逻辑控制部分:此部分由CPLD来完成,实现以下三方面的功能:①对DSP的数据空间进行分时寻址;②产生系统中各个芯片的片选信号;③产生系统中各个芯片的读写信号。

数据通信部分:该部分设计了串口通信以及USB通信两种模式,均可以单独工作。串口通信采用的是TI公司的异步串行收发芯片TL16C550,配合一片MAX232即可实现计算机与目标系统数据的通信;USB通信部分采用了南京沁恒电子公司的USB通信芯片CH375。

1 TMS320VC5402芯片

TMS320VC5402具有优化的CPU结构,内部有1个 40位的算术逻辑单元(包括一个40位的桶式移位寄存器和两个独立的40位累加器),一个17×17的乘法器和一个40位专用加法器,16K×16bit RAM空间和4K×16bit ROM空间;共20根地址线,可寻址64K×16bit数据区和1M×16bit程序区,具有64K I/O空间;处理速度为100MIPS,速度高、功耗低。

评论