基于SOPC的M8051嵌入式调试器设计

引言

在嵌入式系统开发过程中,上位机通过调试器完成对目标机软件的开发、下载、调试。早期的调试器与上位机之间通过串口或并口通信,存在速度慢、通用性差等缺陷。相比之下,USB接口优势明显,具备速度快、易插拔、支持多个调试器同时工作等优势。但目前的USB接口调试器一般采用USB芯片和可编程器件结合的实现方式,成本和复杂度较高。

M8051是Mentor公司的嵌入式8051处理器,凭借良好的性能和功耗控制,占据了大量的SoC(System on a Chip)市场。该处理器集成了OCI(On-Chip Instrumentation,片上调试单元)来完成程序的调试。FS2公司设计的System Navigator是一款针对M8051的调试器,但该产品价格过于昂贵。本文通过研究M8051的调试结构,设计一款基于SOPC(System on a Programmable Chip)的M8051调试器,实现对M8051核心的高效、低成本的开发。

1 M8051片上调试技术的研究

1.1 典型的OCD调试系统

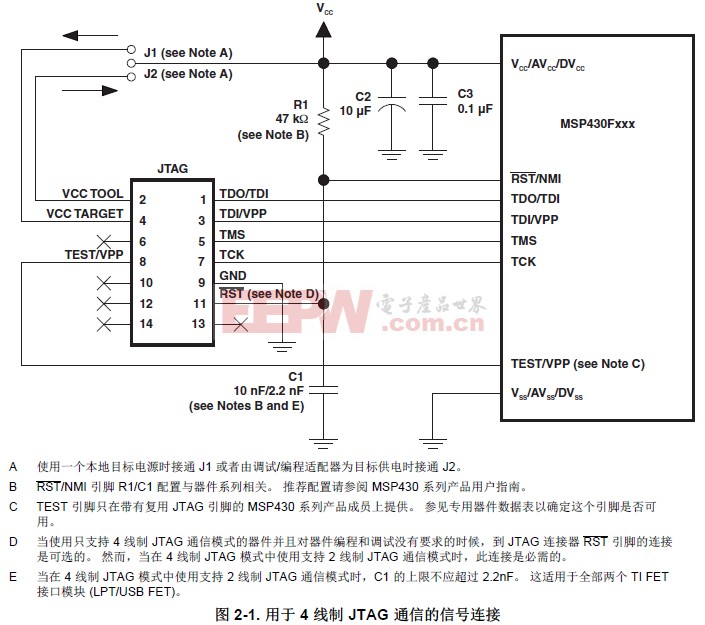

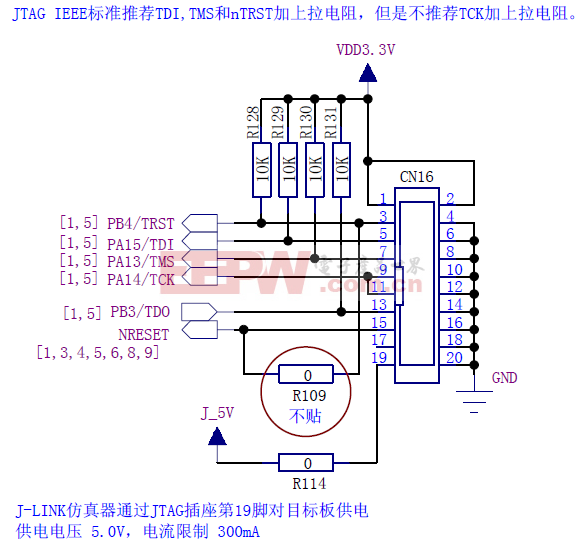

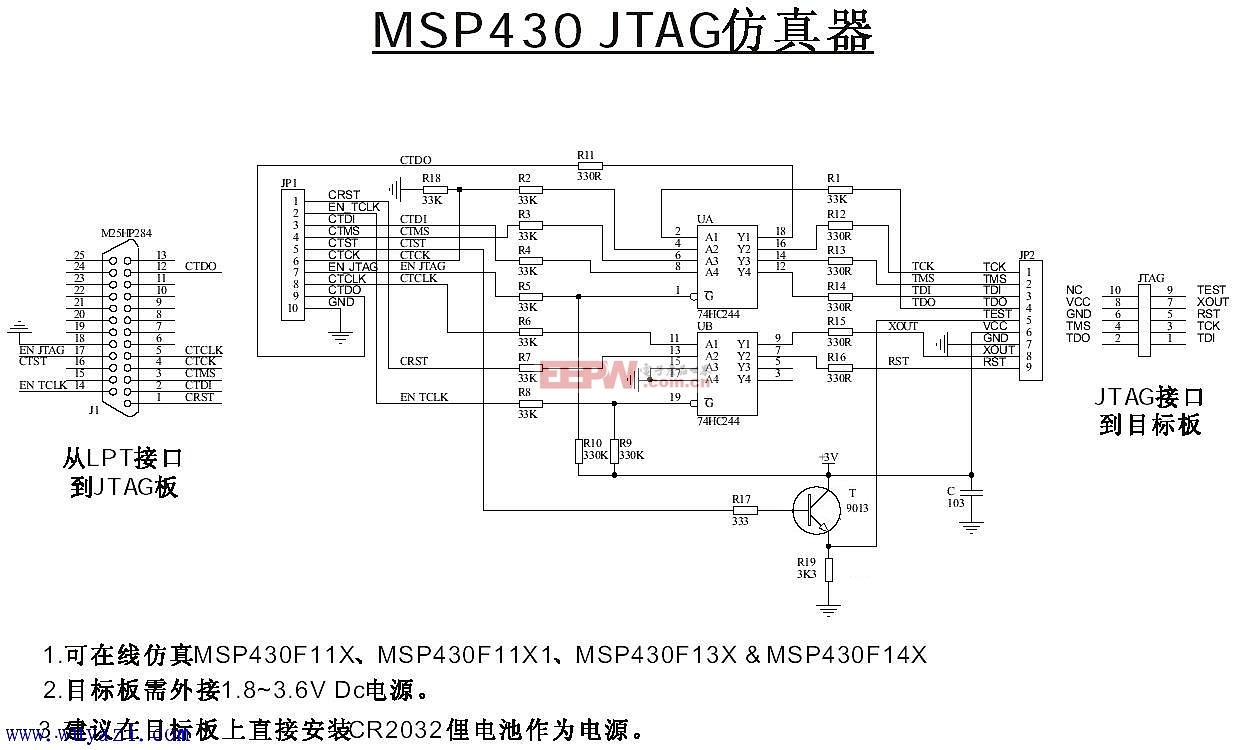

目前,嵌入式调试领域的趋势是在MCU上集成一个专门用于调试的功能模块,并且提供一个专用接口开放给用户。用户通过该调试控制模块来实现停止/继续CPU的运行,并访问目标机上的各种资源,这就是OCD(On-Chip Debug,片上调试)技术。同时,JTAG作为应用最广泛的系统级测试技术,控制逻辑简单、实现方便,常作为片上调试模块的测试接口。

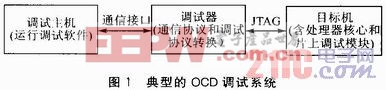

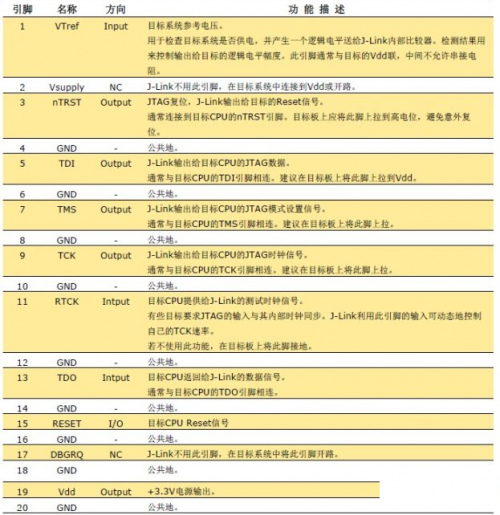

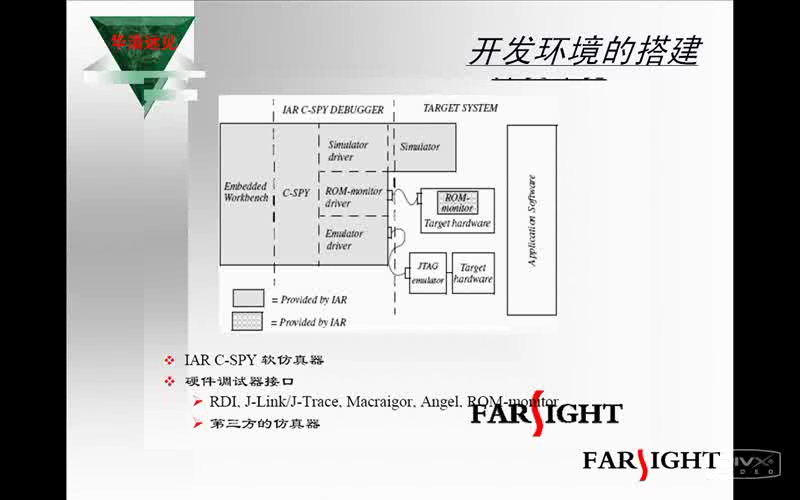

一个完整的OCD调试系统通常包括调试主机、调试协议转换器(或调试器)、目标机三个部分。调试主机运行调试软件,并通过调试器与目标机相连;调试器将主机发出的调试命令和数据转换为基于目标机OCD模块和JTAG接口的调试数据;目标机的OCD模块接收到调试器发来的JTA G数据,完成对CPU的逻辑控制。典型的OCD调试系统如图1所示。

1.2 M8051的片上调试结构

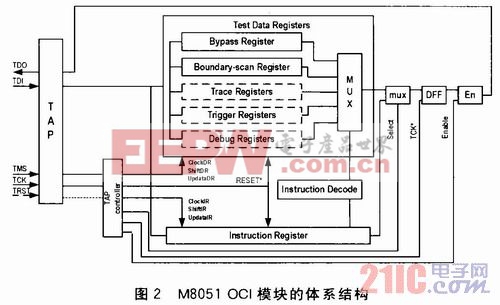

M8051核心的调试功能由其片上的OCI模块完成。OCI模块通过JTAG口与外部通信,其实现完全符合IEEE-1149.1。具体来说,TAP控制器接收一系列的JTAG边界扫描链读写时序,完成对扫描链上的IR和DR的读写。OCI模块内部的Tracc模块、Trigger模块和Dcbug模块根据IR和DR的内容,产生相应的控制信号给处理器,达到控制M8051处理器的运行或者读取处理器信息的目的。以上就是OCI模块的基本调试原理。M805 1OCI模块的体系结构如图2所示。

2 基于SOPC的M8051调试器的设计

2.1 调试系统的总体设计

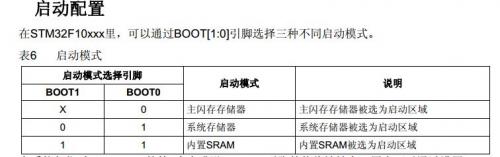

在研究了OCD测试技术和M8051片上调试结构OCI的基础上,本文提出了M8051调试系统的总体设计方案。该方案通过USB接口与上位机通信,调试器主体由一个FPGA芯片实现。其总体结构图如图3所示。

上位机运行调试软件,将编译器的各种调试操作,通过调试接口函数转化为各种调试协议数据;再将这些调试协议数据通过底层通信模块发送给M8051调试器。本设计的底层通信接口是USB接口。编译器选择应用最为广泛的且具备开放调试接口函数AGDI的Keil C51编译器。

M8051调试器本身主要由USB控制器模块、8051处理器和JTAG控制器模块组成。USH控制器在8051处理器的控制下接收来自上位机的调试协议数据;JTAG控制器模块负责将这些调试协议数据转化为基于OCI结构的底层调试命令集,并以JTAG边界扫描链读写时序发送出来。

M8051目标机通过OCI模块的JTAG接口,接收M8051调试器发送的底层调试命令,完成对M8051目标机的调试,并将返回值通过JTAG接口送回M8051调试器。

评论