基于FPGA的通信接口模块的设计

协议使用8B/10B编码保证数据通道的直流平衡,完成时钟的恢复。同时利用8B/10B编码的控制字符作为数据帧传输的起始、结束标识,并作为传输信道的同步控制。在每一数据帧的起始位置添加帧起始控制字符,在数据帧的结束位置添加帧结束控制字符,在数据传输过程中有中断或在无数据传输的空闲时段填充同步控制字符。

控制命令和状态数据都以数据帧的方式在光纤上传输。数据帧格式如图2所示。标识字说明数据帧的性质和传输到的设备,不同的应用有不同的标识,且每个标识有唯一对应的设备,一个设备可能有多个标识字。字长为从标识到校验的长度。数据为命令或状态信息。校验字为从字长到数据的所有字节的循环冗余校验码(CRC)。

2 通信接口模块实现

通信接口模块以FPGA为控制核心,外围添加电平转换芯片实现。通信接口模块对上行控制命令和下行状态信息进行独立处理。在FPGA内实现的逻辑框图如图3所示。

光纤接收和光纤发送模块实现光纤通信协议的物理层处理。成帧和解帧模块实现光纤通信协议的链路层处理。控制命令处理和状态数据处理实现用户数据处理。三线同步串行接口、通用异步串行接口和逻辑电平接口实现针对各个前端受控模块的数据传输。

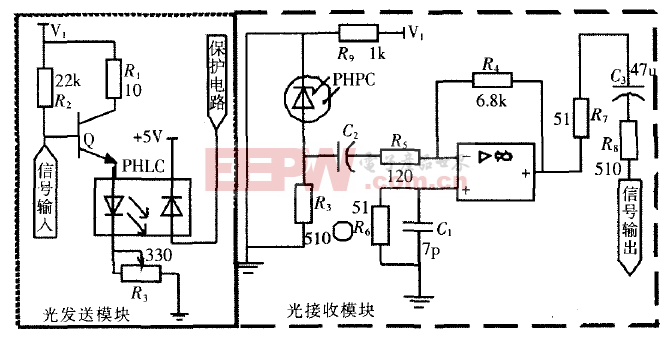

2.1 光纤接口

按照光纤通信协议,光纤接口包括物理层和链路层处理,即图3中的光纤发送/接收、成帧/解帧逻辑模块,发送和接收是相反方向的处理。光纤接收/发送逻辑模块实现串行解串编解码和8B/10B编解码。串行器将并行数据变为串行数据发送至光纤接口;解串器将从光纤接口接收到的串行数据变为并行数据。同时通过8B/10B编码将发送时钟编码到数据中一同发送,解串器则从数据流中恢复时钟。串行器采用

SN65LV1023A器件,解串器采用SN65LV1224B器件。8B/10B编解码则在FPGA中实现。成帧/解帧模块实现数据长度检验、数据校验、添加帧头和帧尾。

2.2 控制命令处理逻辑

控制命令处理逻辑首先检测FIFO缓冲器是否有数据,如有数据则开启一次控制命令处理。数据处理时,根据标志字将数据写入相应的设备接口,一帧数据处理完成后,通过设置帧有效信号,启动接口模块发送。控制状态机如图4所示。

相关推荐

-

herbertwj | 2004-08-15

-

-

xiaohua | 2002-09-24

-

-

-

sandman555 | 2005-02-05

-

-

-

-

sandman555 | 2005-02-05

-

-

-

-

-

-

-

-

sandman555 | 2005-02-05

-

评论