基于ARM9处理器的嵌人式音频系统设计

随着 Internet技术和多媒体技术的快速发展,语音通信技术的应用越来越广泛,也越来越受到重视[1]。如今的嵌人式设备日益复杂化,功能比以前更加丰富,性能也越来越高。在多种嵌人式终端产品中,音频处理功能已成为不可缺少的重要组成部分,高质量的音效是当前发展的重要趋势。

本文利用 ATMEL公司 的 AT91RM9200型微处理器 和 Philips公司的 UDA1341型立体声音频编解码器设计了一种嵌入式音频系统。该嵌入式音频系统硬件部分采用基于IIS总线的音频系统体系结构,其主要硬件电路后文作了详细的介绍。软件上,笔者以嵌入式Linux操作系统作为平台,重点介绍该音频系统在此平台下的驱动程序的实现。

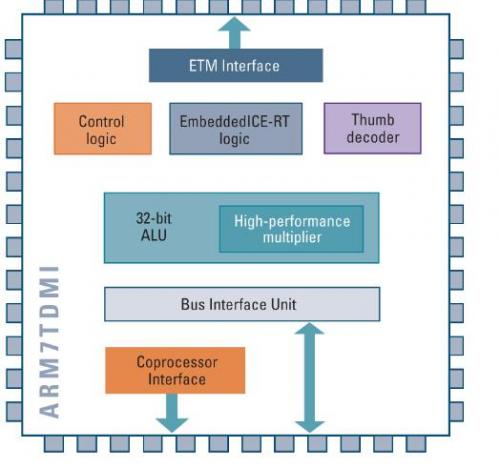

2 AT91RM9200处理器简介

AT91RM9200是 ATMEL公司针对系统控制以及通信领域推出的基于ARM920T内核的新型微处理器[2],在高性能和低功耗特性方面具有极大的优势,而且具有很高的主频,最高可达到180 MHz。该处理器具有独立的16K指令和16K数据cache,全功能的MMU虚拟内存管理单元,以及内部的16KB SRAM和128KB ROM,EBI接口控制器。片上集成了丰富的外围接口,包括网络MAC、USB控制器、SDRAM 控制器、CF接口、NAND flash接口、IIC接口、JTAG调试器以及支持 256 MB的地址空间。而且处理器还提供自举模式,供用户写入引导代码,方便 Linux等操作系统的移植。

3 UDA1341TS音频芯片及IIS总线简介

Philips公司的 UDA1341TS是一块功能强大的专用语音处理芯片[3]。该芯片集语音放大、滤波、采样、A/D和D/A转换等功能于一体,并且能进行数字语音处理。本设计使用的AT91RM9200处理器具有一个IIS音频接口,此接口采用 DMA方式传输数据。在该方式下,由DMA控制器取代CPU,获得总线控制权,从而实现内存与外设或者内存之间的不同区域之间大量数据的快速传输。用DMA接口传输数据,不仅可以降低CPU负担,还可以节省系统的软件设计时间,降低编程难度。而 UDA1341TS支持IIS总线格式,并且具有数字语音处理特性,由此决定了UDA1341TS与AT91RM9200处理器的电路连接比较简单,并且能实现语音的 A/D和 D/A等预处理,而不需要再额外增加专门的A/D和 D/A器件。

需要说明的是,数字音频系统需要多种多样的集成电路,因此,为这些电路提供一个标准的通信协议非常重要。IIS总线是由SONY和PHILIPS公司等电子巨头共同提出的数字音频总线协议,全称是内部集成电路声音总线 (Inter IC Sound Bus),它是一种串行的数字音频总线协议,该总线专门用于音频设备之间的数据传输,为数字立体声提供一个序列连接至标准编解码器[4],目前很多音频芯片和处理器都提供了对IIS总线的支持。笔者根据IIS总线的原理,结合AT91RM9200处理器和数字音频输入/输出接口芯片 UDA1341TS的结构特点,设计的嵌入式音频系统可以运用到很多类似的音频系统中。

4 系统硬件设计方案

由于IIS总线只处理音频数据,而其他的信号如编码、控制等信号单独传送。为了使必需的引脚数最小并且保持连线简单,IIS总线由3条信号线组成:时分复用的数据通道线、字段选择线和时钟信号线。本系统由系统主控制器提供时钟信号,控制数字音频数据在各个IC之间的流向。此时,发送器在外部时钟信号的控制下产生数据,处于从模式。

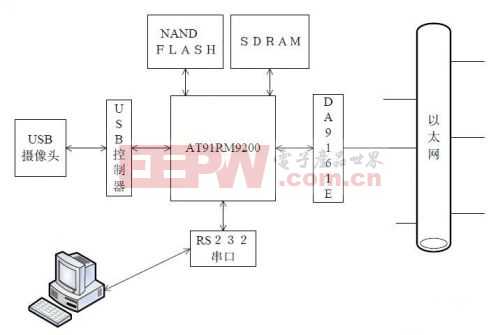

本设计硬件连接图比较简单,如图1所示。图中的处理器采用了AT91RM9200处理器,其内置IIS音频总线,内置的IIS接口能读取IIS总线上的数据,并由UDA1341TS芯片外扩,通过总线和系统连接,需要处理器提供系统时钟和3根控制线。

图1 硬件设计简图

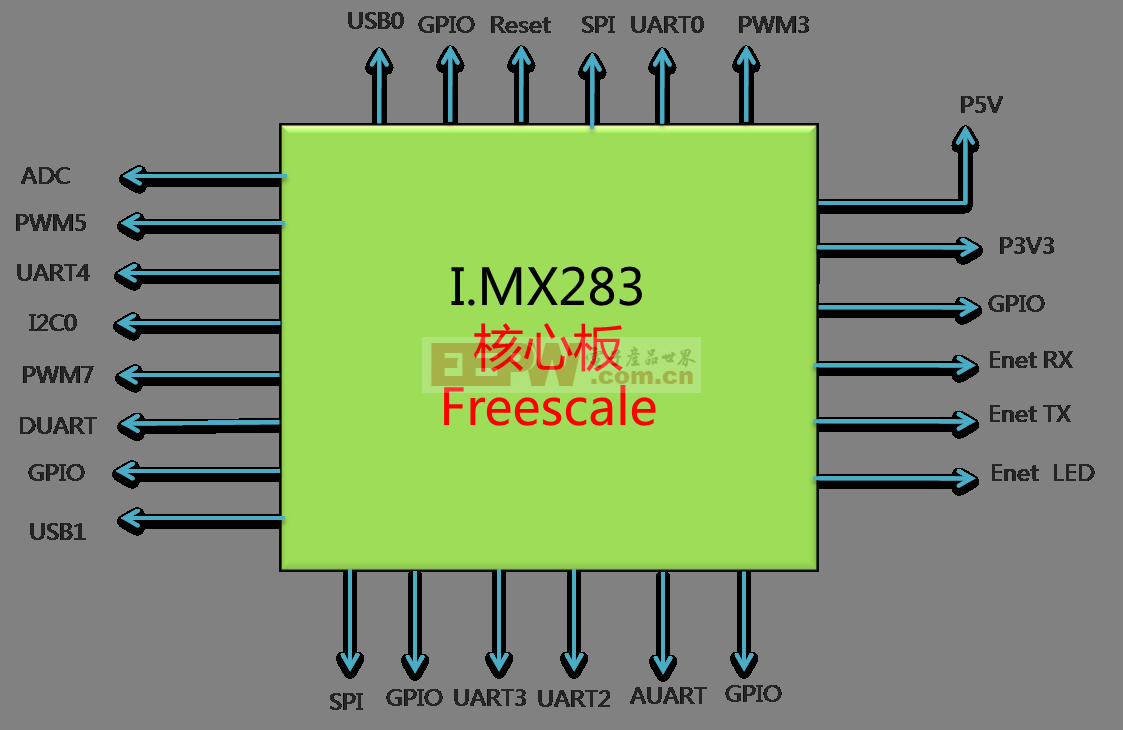

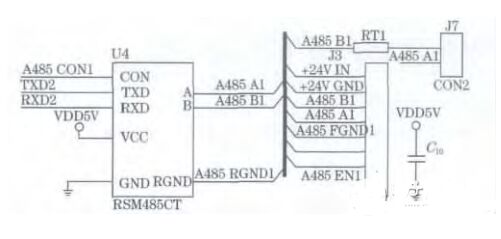

AT91RM9200的IIS控制器由5个引脚与外部的音频编解码器相连。这些引脚分别是:系统时钟;位速率时钟(可使用内部或外部时钟源);字段选择;串行声音输入;串行声音输出。本设计中,UDA1341TS使用的是L3接口 ,该接口用来控制音频信号的音量大小以及低音等。L3接口有3个信号:L3MODE,L3CLK,L3DATA,将字节写入 L3总线寄存器。IIS总线控制器通过软件控制AT91RM9200的通用I/O引脚(笔者选用的是PA0、PA1、PA2三个通用I/O口)来支持L3接口。下图是本嵌入式音频系统的硬件电路连接图,见图2

评论