I2C总线驱动在嵌入式系统中的两种实现

1 引 言

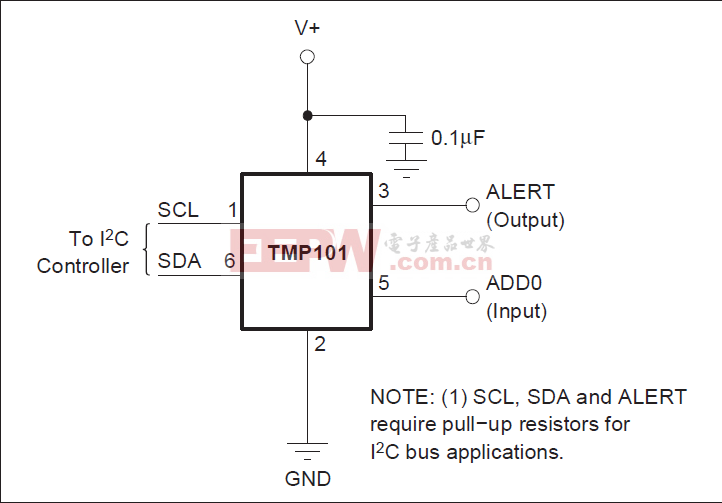

I2C总线(Inter-IC Bus)是一种通用的串行总线,是用于IC器件之间连接的二线制总线。他通过串行数据线(Serial Data Lines,SDL)及串行时钟线(Serial ClockLine,SCL)两线在连接到总线上的器件之间传送信息,并根据地址识别每个器件。一个或多个微控制器以及外围器件可以通过I2C总线接口非常方便的连接在一起构成系统。这种总线结构的连线和连接引脚少,器件间总线简单。结构紧凑,因此其构成系统的成本较低;并且在总线上增加器件不会影响系统的正常工作,所有的I。C器件共用一套总线,因此其系统修改和可扩展性好。即使有不同时钟速度的器件连接到总线上,时间同步机制也能够很方便地确定总线时钟,因此在嵌入式系统中得到了广泛的应用。 2 I2C总线原理

2.1 I2C工作原理

I2C总线是由数据线SDA和时钟线SCL构成的串行总线,可发送和接收数据。每个连接到总线的器件都可以通过惟一的地址与主机通讯,主机可以作为主机发送器或主机接收器。他是一个真正的多主机总线,如果两个或更多主机同时初始化,数据传输可以通过冲突检测和仲裁防止数据被破坏。串行的8位双向数据传输位速率在标准模式下可达100 kb/s,快速模式下可达400 kb/s,高速模式下可达3.4 Mb/s。连接到相同总线的IC数量只受到总线的最大电容400 pF限制。

I2C总线在传送数据过程中共有3种特殊的电平变换情况,他们分别是:起始(start)、停止(stop)和响应(aek)。

当SCL为高电平时,SDA由高电平向低电平跳变,这个表示起始条件;当SCL是高电平时,SDA线由低电平向高电平跳变表示停止条件。起始和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态,在停止条件的某段时间后总线被认为再次处于空闲状态。

响应信号是指从机在接收到8b数据后,向主机发出特定的低电平脉冲,表示已收到数据。在响应的时钟脉冲期间,从机必须将SDA线拉低使他在这个时钟脉冲的高电平期间保持稳定的低电平,主机收到应答信号后,根据实际情况做出是否继续传递信号的判断。若未收到应答信号,则判断为从机出现故障。

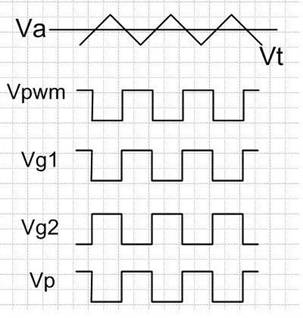

2.2操作时序

I2C总线运用主/从双向通讯。主机和从机都可以工作于接收和发送状态。总线必须由主机(通常为微控制器)控制,主机产生串行时钟(SCL)控制总线的传输方向,并产生起始和停止条件。SDA线上的数据状态仅在SCL为低电平的期间才能改变,SCL为高电平的期间,SDA状态的改变被用来表示起始和停止条件。具体时序见图1。

3嵌入式系统中的I2C驱动的两种实现

3.1 系统自带I2C寄存器的实现

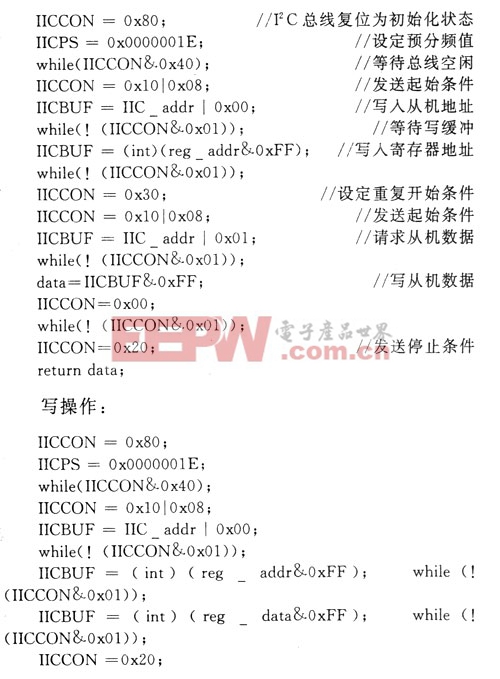

下面以ARM S3C4510B为例,给出基于寄存器方式的I2C驱动实现。S3C4510B内含一个I2C总线主控器,可方便地与各种带有I2C接口的器件相连。I2C总线控制器有3个特殊功能寄存器:一个控制状态寄存器(I2CON),一个预分频寄存器(I2CPS)和一个移位缓冲寄存器(I2CBUF)。通过配置这些寄存器,可实现正确的I2C数据传输时序。下面分别给出读、写实现的实例。读操作:

写数据的操作 先设置控制状态寄存器的BF位(0x01),然后写入数据到移位缓冲寄存器。移位缓冲寄存器无论是被读还是写,BF位均会自动清零。若要进行连续的读/写操作,必须设置控制状态寄存器的ACK位(0x08)。

读数据的操作 在设置控制状态寄存器的BF位以后,可以进行读数据的操作,当读/写完最后一个字节时,可对ACK位进行复位通知发送器/接收器读数据操作结束。

在读/写操作完成以后,可通过对I2CCON写入0x20生成结束码。

评论