基于ATMEGA128的自动准同期装置设计

具体而言,交流信号用 表示。下面是计算的详细过程。

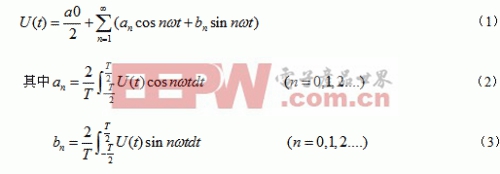

将周期信号展开成为傅立叶级数的形式:

当 时,可以推出

由7式可以看出只要求 和,就可以求出基波的最大值和有效值。同理可以求出其他高次谐波的相关值。将公式2和公式3离散化,则可以在程序中实现计算。也就是

其中,N为同步采样点数。

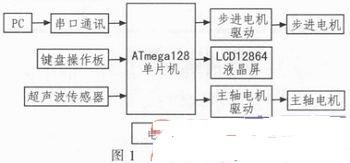

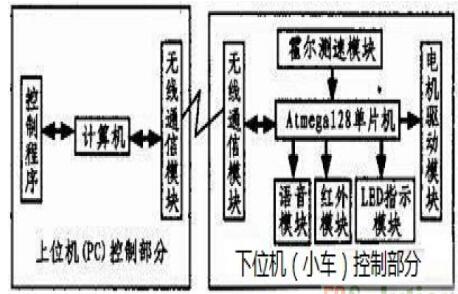

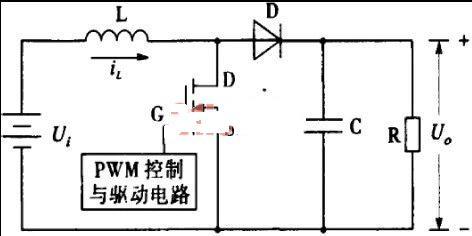

相角的测量有两种实现途径。一种是主要依赖硬件,软件起辅助作用。另一种则完全依赖软件,采用不同的算法。前者的误差主要来自硬件,后者的误差主要是算法所带来的。Atmega128的16位定时器T1/C1和T3/C3均具有输入捕获的功能,可以利用两者对两侧交流信号上升沿进行捕获,捕获的时间差与周期进行比较,就可以折算出两者之间的相差。

但是,迟滞比较器的存在使输出对输入信号的幅值敏感,输入信号幅值越大,相移越小,也就是说在电压比较低的时候,误差会比较大。完全依赖软件的测量办法很多,本装置的实现方法如下:

则它们的相位差为 。可以推导

根据公式18,可求出相差。为了更高精度,可以展开成为高阶级数。

3 同期过程流程图

笔者所设计的同期装置的同期过程见上图所示。其中,频率要优先调节。频差在要求范围内时,才可以转去调节电压。每次同期操作要设定同期时限,在规定时间内各项指标不能达到定值要求,则此次同期操作失败。

总结

本文介绍的准同期装置设计方案最大程度利用了硬件资源,减少了软件误差。装置投入使用后经过测试可以达到机组开关的同期要求,有一定推广价值。

评论