基于VLSI 平台的AVR 处理器仿真与设计

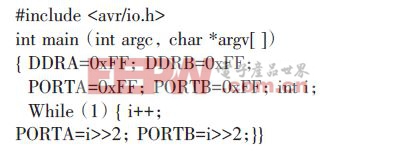

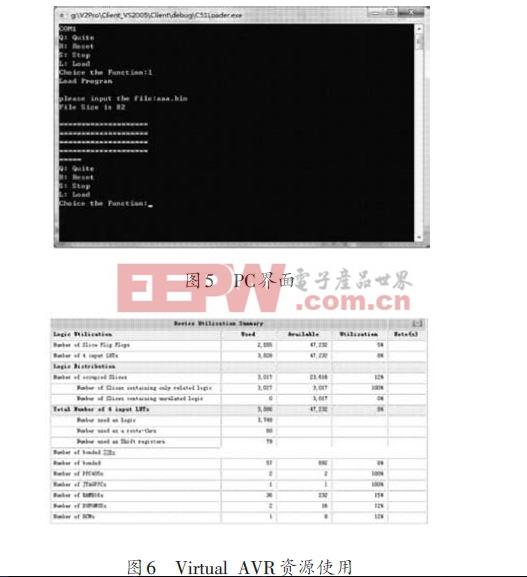

使用WINAVR-GCC 编译工具,编译生成HEX 文件,后再转化为BIN文件,将该BIN文件通过EDK组建更新ROM,观察硬件LED,如图7所示,其正常工作,Vir-tual AVR得到验证。

5 结语

随着MCU 应用范围越来越宽,对MCU 要求也提高,尤其目前MCU逐渐进入SoC时代,IP核复用将成为主流设计方法。为使老一代MCU延续生命力,开发其兼容IP核,不仅能将以往代码迅速移植到新系统,且可加快新系统开发,将以往很多分立器件用逻辑功能实现,集成于ASIC中,降低外围硬件电路的设计。文中从模拟MCU核开始,阐述了用FPGA来虚拟出传统MCU的设计原理和方法,适度改变内部结构,添加Wishbone总线,替代传统MCU片内总线,来完成MCU核与外设的连接,使传统MCU变的更灵活。结果表明,实现了既定目标,与标准的微控制器兼容,系统运行稳定。该方法延续了传统微控制器的生命力,能使其得到更大发展。由于Wishbone总线支持多主设备,今后可在一个FPGA 中集成多个MCU核,对于性能的提升将是质的飞跃

评论