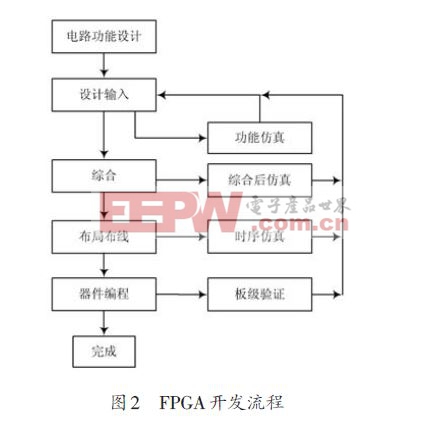

基于VLSI 平台的AVR 处理器仿真与设计

3 Virtual AVR 实现

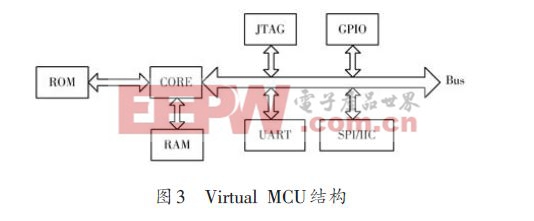

通过对FPGA和MCU的深入了解,可知使用FPGA的丰富资源来虚拟出MCU是完全可行的。首先,需设计一个总体结构,如图3所示。ROM用于存放被执行程序及二进制代码,RAM 为运行内存,用总线将VirtualMCU Core与各外设相连。使用该结构可简化设计,无需对外设重复设计,只要使Virtual MCU Core满足同一接口即可。

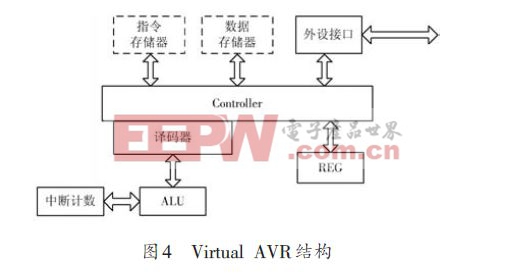

Virtual MCU Core由几部分构成:算术逻辑单元,运算的主要单元;译码器,由二进制文件判断指令类型并获得源操作数和目的操作数等;寄存器,用于参加运算和存储某些中间值等。

Virtual AVR Core 以ATmega103处理器为参考,核心采用RISC结构,3级流水线结构,因为是哈佛结构,所以分为数据存储器和指令存储器。它的处理器核心如图4所示。同时ATmega103共有130条指令,每条指令都是固定结构,为16 位。在该设计中,移植了Open-Cores开源组织的8位AVR核,它支持3级流水线,兼容标准AVR微处理器。

ALU的实现采用模块化设计,共分为控制模块、加减法模块和乘除法模块。3级流水线设计如下:

stage0:FETCH,给出指令地址,并读取相应的指令,主要由译码机构负责;stage1:ALU/MEM,ALU运算,或数据存储器操作,读数据存储器时,在地址总线上给出正确的值,当写数据存储器时,不仅需要提供正确的地址,还需要在数据总线上提供正确的数据,主要由运算机构和总线控制机构负责。

Stage2:LOAD,从数据线上获取数据,存至寄存器中,主要由寄存器机构负责。

在一个系统中光有处理器是不够的,需要有丰富的外设来满足各种控制要求或数据传输功能,而片内总线便是将处理器与总线连接的重要途径。文中采用Sili-core的Wishbone总线进行设计,具有简单、开放、高效和方便实现等特点,且完全开放并没有专利保护。Wish-bone有四种连接模式:点对点、数据流、共享总线和十字交叉互联。文中使用共享总线连接方式,其中充当Master为Virtual Core,而外设为Slaver.

为使Virtual Core能与外部器件进行通信,需要外设的支持。外设按数据流类型分为串行和并行,常用的串行外设有SPI、I2C、UART 等,常用的并行外设有GPIO等。

4 硬件支持与测试

硬件环境主要分为两部分:第一部分为核心板,用以支持Virtex-Ⅱ Pro的运行;第二部分为底板,主要为添加外设环境,丰富系统的功能。选用XC2VP50FFG1152芯片作为核心的FPGA,在外围又添加了DDR和SDRAM,方便自由选择存储器类型。FP-GA掉电后,内容自动消失,每上电需要重新配置,为让FPGA 上电后自动配置,需加一片PROM,使用XCF32P.FPGA采用并行主模式。底板上则是增加大量外设:UART、PS2、VGA、ETHERNET、VIDEO、A/D、D/A、SD、USB等。

Virtual Core执行的程序都是固化在ROM中,为达到测试要求,要多次更新ROM中内容,为此使用嵌入式开发套件(Embedded Development Kit,EDK)来开发一个测试工具。首先将BRAM配置为双端口RAM,一端口给Virtual Core来进行读取操作,一端口给EDK,来更新程序存储器。同时EDK也可提供简单的控制任务,如重启Virtual Core 等,EDK 使用UART 和计算机进行操作。为方便控制,设计一个较为简单的PC端串口程序,用于将EDK与PC交互,主要是将用户的命令或文件经串口发送至EDK,如图5所示。搭建一个简易测试系统,使用ISE工具,进行综合布局布线,其资源消耗如图6所示。编写一个跑马灯程序,代码如下:

评论