基于VerilogHDL的FIR数字滤波器设计与仿真

2、Verilog HDL代码编写风格

HDL代码编写应该具有很好的易读性和可重用性,而自顶向下的分割方法可以帮助我们达到最佳的结果。HDL代码在达到功能的情况下要尽可能的简洁,尽量避免使用带有特殊库单元的实例,因为这样会使得整个进程变得不可靠。

在本设计中,我们将设计划分成一个顶级文件和三个次级文件,并且调用了QuartusII中的MegaFunction功能辅助完成整个设计。

图3显示FIR滤波器的顶级方块图

表1:FIR滤波器的设计范例的端口列表

3、验证仿真

完全可综合设计的一个优点就是同样的HDL代码能够用于验证和综合。在使用HDL代码之前必须要验证设计的功能,最好且最简单的方法就是利用验证工具,其次是利用仿真工具作有目的的仿真。

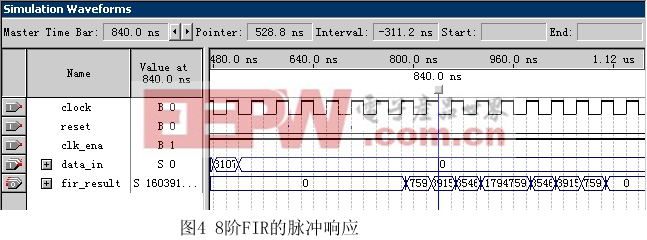

QuartusII内部带有仿真器,只要通过建立正确的Vector Waveform File(向量波形文件)就可以开始仿真了。图4所示为QuartusII内部仿真器得到的8阶FIR的脉冲响应波形。

五、结论

利用Verilog HDL设计数字滤波器的最大优点就是可使设计更加灵活。比较硬件电路图设计,Verilog HDL语言设计的参数可以很容易在Verilog程序中更改,通过综合工具的简化和综合即可以得到电路图,其效率要高出利用卡诺图进行人工设计许多。而且编译过程也非常简单高效。优秀编码风格能够在综合过程中节省芯片使用的单元,从而降低设计成本。

参考文献:

[1]. 夏宇闻。VerilogHDL数字系统设计教程,北京航空航天大学出版社,北京. 2003.

[2]. Altera Corporation. Introduction to QuartusII. 2003

[3]. Michael D. Ciletti. Advanced Digital Design with Verilog HDL. Prentice Hall, NJ.2005.

[4].彭保等.基于VerilogHDL的FPGA设计. 微计算机信息, 2004年第20卷第10期

评论