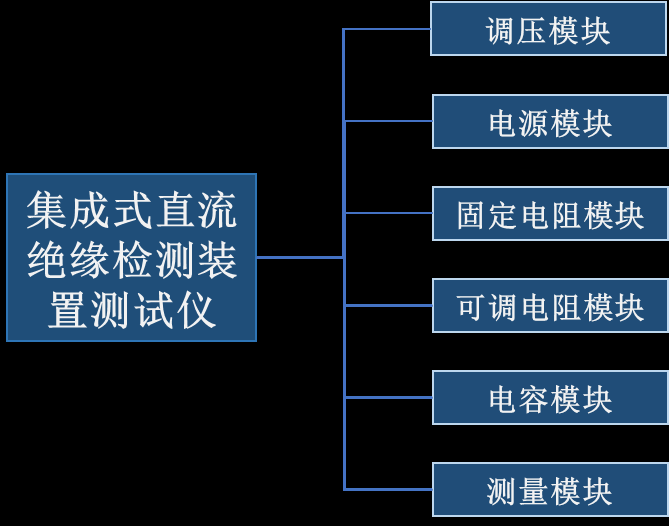

集成运放参数测试仪设计方案

所以:

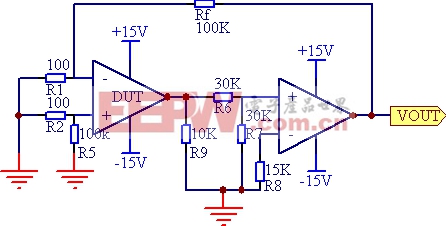

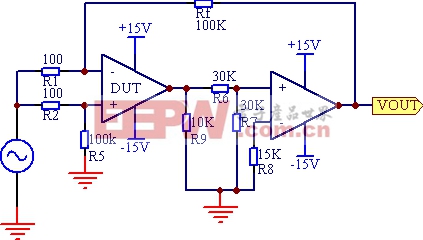

图4-1-2 开环放大倍数测量原理图

(二)输入失调电压的测量

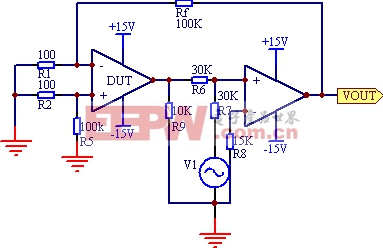

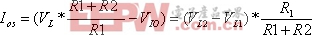

继电器状态:K1,K2接地,K3,K4接通,K5,K6接地。如图 4-2-1

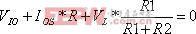

K6接地,放大器U1的输出与放大器U2的同相端通过一电阻分压网络相连,而放大器U2的反相端接地。所以: 根据输入失调电压的定义:

根据输入失调电压的定义: (

( )

)

图4-2-1 输入失调电压测试原理图

(三)输入失调电流的测量

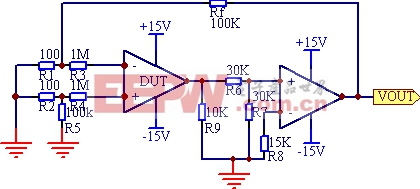

继电器状态:K1,K2接地,K3,K4断开,K5,K6接地。如图4-3-1

与上面相同有 ,所以有:

,所以有:

图4-3-1 输入失调电流测试原理图

(四)共模抑制比的测量

继电器状态:K1、K2接信号端,K3、K4闭合。K5,K6接地。如图4-4-1运放应对共模信号有很强的抑制能力。表征这种能力的参数叫共模抑制比,用kCMR表示。它定义为差模电压增益AvD和共模电压增益Avc之比,即kCMR=∣AvD/Avc∣。

测试原理如图35.5所示。由于RF>>RI,该闭环电路对差模信号的增益AvD= RF/RI。共模信号的增益AvC= (VO/VS)。因此,只要从电路上测出VO和VS,即可求出共模抑制比

KCMR=∣AvD/Avc∣= (RF/RI)o(VS/VO)

KCMR的大小往往与频率有关,同时也与输入信号大小和波形有关。测量的频率不宜太高,信号不宜太大。

图4-4-1 共模抑制比测量原理图

(五) -3dB带宽F0

继电器状态:K7断开,K4闭合,K2接信号端;被测放大器构成单位增益状态。K9接OUT1将单位增益状态的放大器信号输出。

-3dB带宽的测量,通过FPGA与外部锁相环对30MHz信号进行程控分频与倍频,产生高精确度的扫频信号,然后通过隔直电容加到被测放大器的同相输入端(放大器通过继电器切换接成单位增益组态),放大器的输出信号通过隔直电容加到有效值转换芯片的输入端。扫频信号从40kHz开始逐渐增大,同时通过AD检测有效值转换芯片的输出电压,当输出电压下降到原来的0.707倍时记下此时的频率值既是-3dB带宽截止频率。

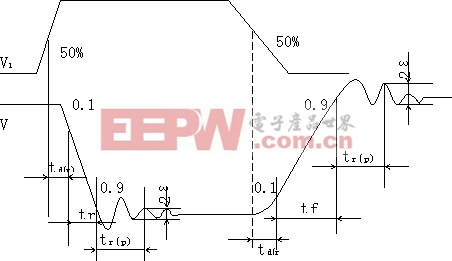

(六)转换速率(SR)和上升时间的测量

脉冲响应时间包括上升时间,下降时间、延迟时间、和脉动时间等。测试电路仍然采用以上电路,继电器状态K7断开,K4闭合,K2接信号端;被测放大器构成单位增益状态。K9接OUT1将单位增益状态的放大器信号输出。读取响应时间方法如下图所示。其中tr为上升时间,tf为下降时间,td(r)为上升延迟时间,td(f)为下降延迟时间。在单片机的控制下,FPGA发出一阶跃信号,同时触发高速计数,通过一高速比较器检测放大器的输出状态,当上升到0.9Vdd时锁存计数值,同时触发中断,将计数值送给单片机。单片机根据此计数值和计数频率便可以计算出上升时间。

图4-6-1 Tr示意图

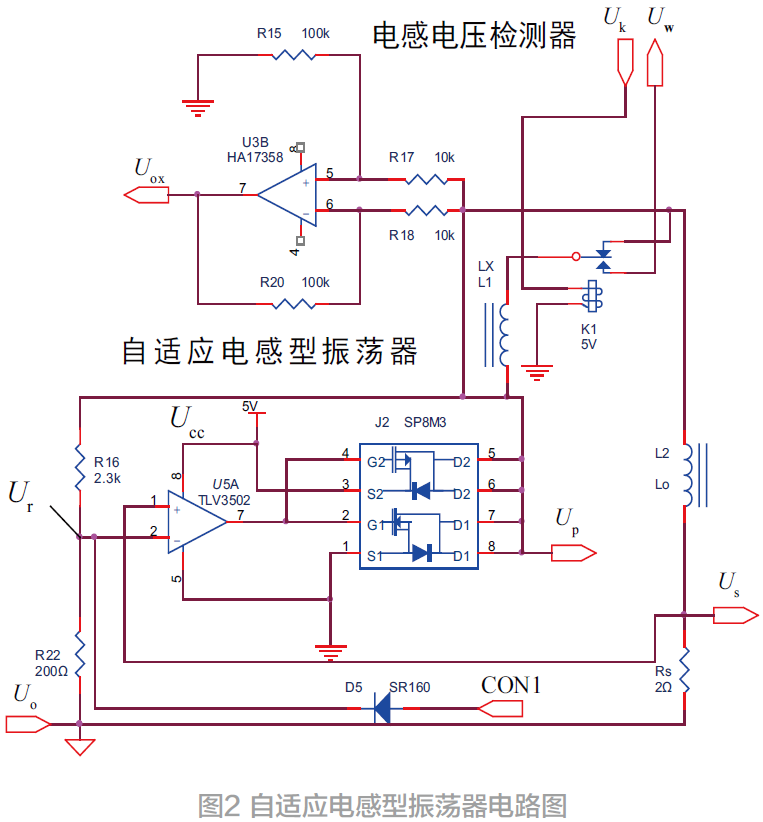

五、电路图及有关设计文件

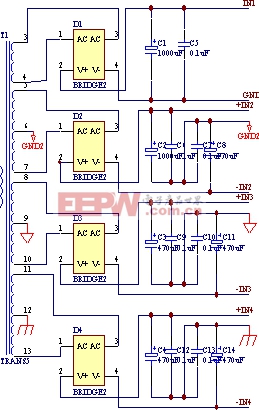

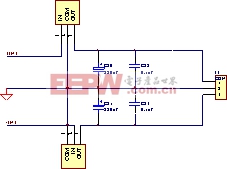

(一)电源电路:

为了保证足够的电源供应,我们制作了一个有±5V、±12V、±15V、0~30V可调的电压源。 图5-1-1、图5-1-2是原理图

图5-1-1 电源电路

评论