集成运放参数测试仪设计方案

经过综合考虑我们选择方案二,不需要很复杂的电路就可以实现并扩展非常强大的显示功能。

2、 键盘输入方案:

方案一:采用7289芯片与键盘相结合,键盘的整个控制只需4条控制线。程序的编写也比较简单且容易同led显示接口。

方案二:不使用任何专用芯片,用一块74LS138译码输出8路扫描信号,3路扫描返回信号线接I/O口输入(我们设计的是3*8的键盘)。这种设计方案电路设计非常的简单,但是软件的编写要考虑软件去抖等,会比较复杂而且占用大量的CPU资源。

方案三:在FPGA内部构造一键盘扫描控制器,专门用以处理按键信息,并进行初步的处理(如键盘去抖),通过中断把键值发送给单片机。由于我们在FPGA内部已经建立了系统总线,扩展键盘非常简单。而且采用此方法外部硬件电路的设计也非常简单。

比较三者的优缺点我们选择了方案三,这样充分利用CPLD的功能硬件与软件设计都比较简单。二、整机工作原理与功能实现

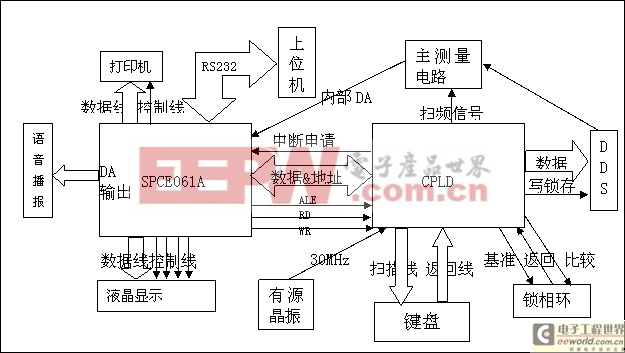

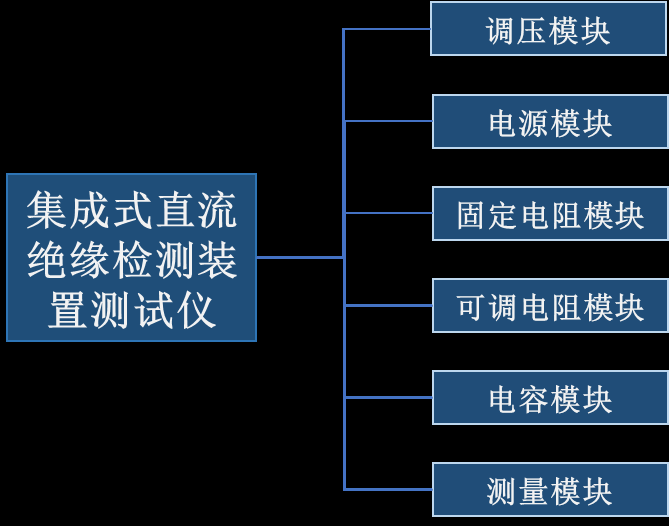

图2-1-1 系统整体结构示意图

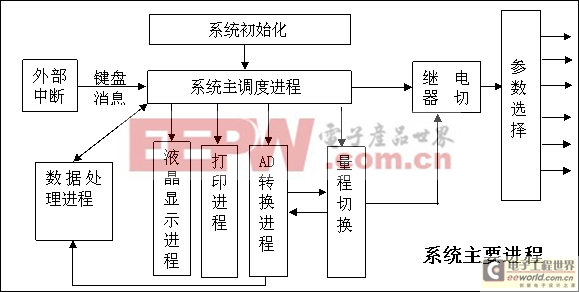

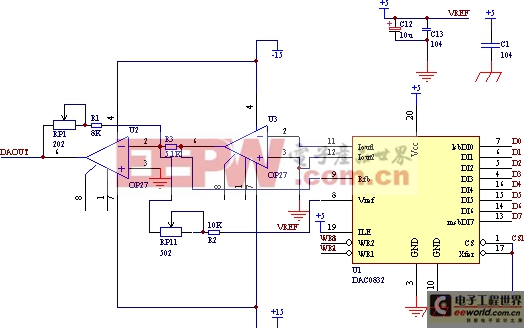

图2-1-1 系统整体结构示意图 系统电路原理图如图5-3-1所示。通过继电器的切换实现四个基本参数和大量程的转换。测量开环放大倍数和共模抑制比的基准信号采用DDS合成技术产生(DDS合成控制器通过硬件编程在FPGA内部生成)。信号的幅值通过精密整流后的响应信号高速采样,再经过数字信号处理的方法获得。采样信号的幅值测量采用等精度测量方法,通过程控放大器将采样信号的幅度控制在1-3.3V之间,这样可以使小信号测量时有效位数增多,又克服了测量大信号量程不足的限制。

-3dB带宽的测量,通过FPGA与外部锁相环对30MHz信号进行分频与倍频,产生高精确度的扫频信号,然后通过隔直电容加到被测放大器的同相输入端(放大器通过继电器切换接成单位增益组态),放大器的输出信号通过隔直电容加到有效值转换芯片的输入端。扫频信号从40kHz开始逐渐增大,同时通过AD检测有效值转换芯片的输出电压,当输出电压下降到原来的0.707倍时记下此时的频率值既是-3dB带宽截止频率。

上升时间的测量,单片机向某一特定地址中写入任意值,启动上升时间测量功能。接着FPGA输出一阶跃信号给被测放大器(被测放大器也接成单位增益组态),同时启动高速计数,放大器的输出信号送给一比较电平设为0.9Vdd的高速比较器,当放大器输出端的信号增大到0.9Vdd时比较器输出高电平,FPGA内部计数器停止计数。如图2-1-2根据此计数值和计数时钟的频率便可以得到上升时间。

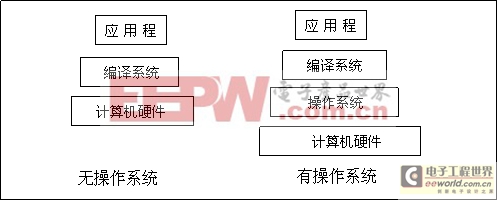

图2-2-1无操作系统与有操作系统的区别

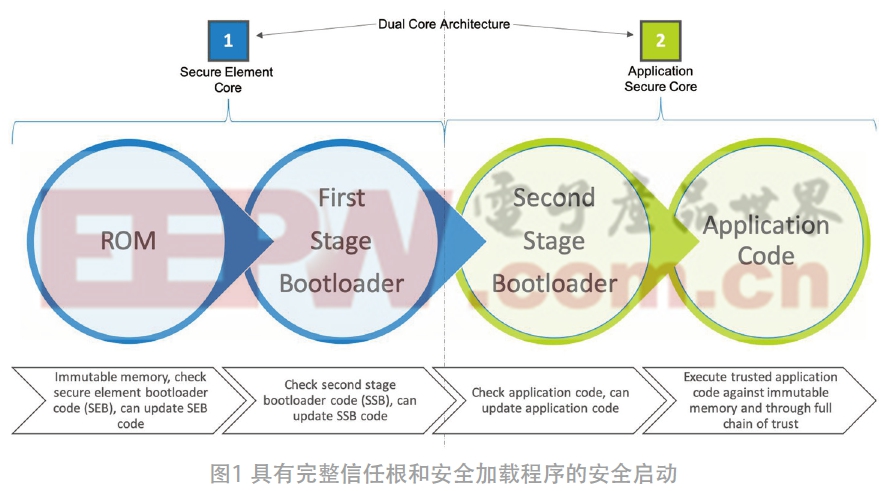

设计到很多的硬件、软件及其混合的设计。采用操作系统的架构来组织,将非常有利于我们小组各个成员之间的协作开发。有的人专注于服务进程以及用户界面和数据处理,有人专注于FPGA系统总线和外围器件以及底层驱动程序的设计。

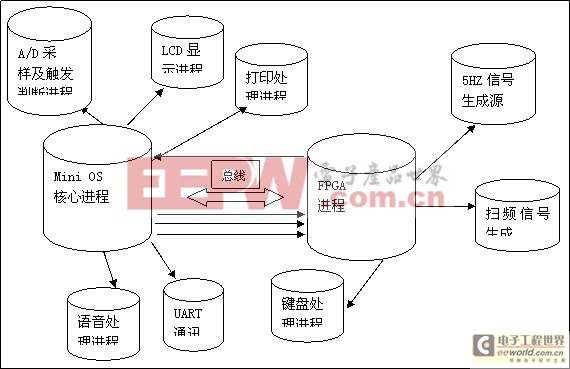

Mini OS是一款拥有可裁剪、多任务的占先式内核的操作系统。它的任务调用及中断时间是可知道的,因此,采用Mini OS操作系统将大幅改善软件设计的环境,提高软件设计的规范。且该系统的底层模块完全采用汇编语言编写,然后采用操作系统调度的方法,很大程度上提高了系统的实时性和执行效率。如图2-2-2

图2-2-2 Mini OS 各进程示意图 (三)其他系统扩展

(三)其他系统扩展

1、语音播报方案

为了丰富人机的接口我们增加了语音的播报利用 凌阳SPCE061位单片机的语音处理功能。只须调用库函数即可以实现音频编程或自己录制语音资源就可以实现语音播放以及语音报警功能。

2、打印功能

为了能够将测量数据打印出来,我们采用了TL58打印机,该打印机小型、轻便、我们使用并口打印,控制也非常的方便。它带国家一、二级字库,可以满足一般打印的需求。

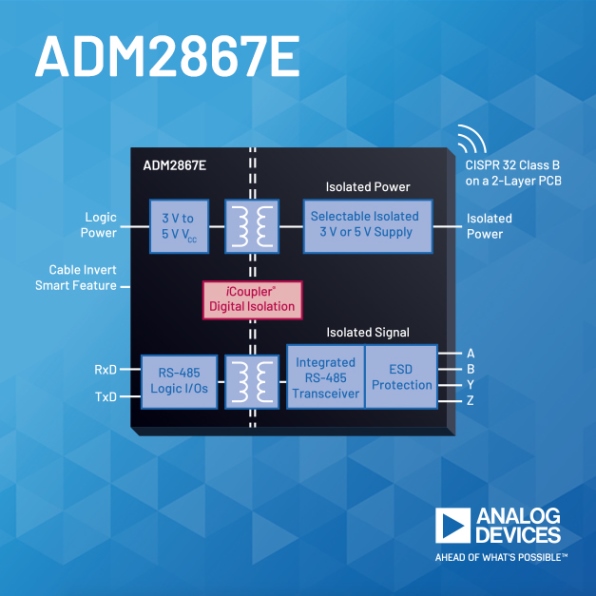

3、串口通信功能

为了适应网络化的趋势,为了能够进行大批量的数据统计与分析我们设计了此与上位机进行通讯的串行数据接口。我们可以通过此串行接口,将一批运放的测量参数上传到上位机,然后进行统计分析,对这一批运放的性能参数给出有效的估计。这在实际的科研、生产中比只测量一两个放大器的参数具有更大的意义。我们还可以通过上位机控制下位机测量相应的参数,并在显示屏上显示下位机无法显示的参数(如波特图、对正弦信号相应的频谱)具有虚拟仪器的功能。

三、各子模块的设计

(一)输入电压4~40mV、输入电流0~4mA量程转换:

量程转换通过继电器和程控放大器相结合实现。继电器切换大量程;程控放大器切换小量程,最终将信号的幅度控制在1-3.3V之间,这样既可以使小信号测量时有效位数增多,又克服了测量大信号量程不足的限制;保证了测量的精度和范围,实现等精度测量。

图3-3-1 DDS外围电路 (四)单位增益带宽测试:

在该功能中需要40KHZ--4MHZ的扫频信号,我们通过FPGA和外部锁相环对30MHz的系统时钟进行程控分频和倍频生成,从而使产生的频率可以进行数字控制,而且极其稳定。为了测试放大器的截止频率,我们需要检测单位增益组态的放大器对扫频信号的响应情况。对于如此高频的信号我们不能采用A/D采样方法处理了,而是采用RMS真有效值转换的芯片,进过实验的测试我们最终选用AD637芯片。它的标定响应频率为6MHZ。我们对其进行了检测,该芯片完全符合我们的需求。 图3-1-1 程控放大器原理图(自动量程转换)

图3-1-1 程控放大器原理图(自动量程转换)

(二)静态参数与动态参数的

评论