异步二进制加法计数器时序分析

计数器是一种常用的数字部件,是触发器的重要应用之一。顾名思义,计数器就是能够累计输入脉冲数目的数字电路。它是一种记忆系统,除用作计数外,还可用作分频、定时等。

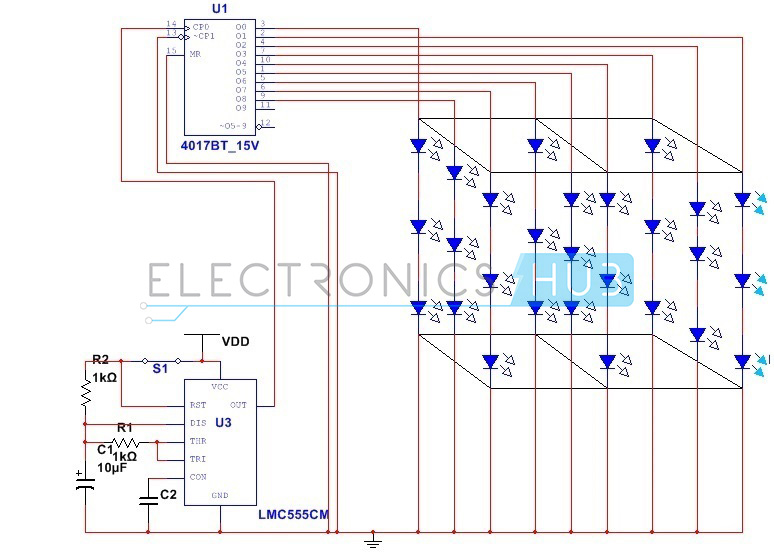

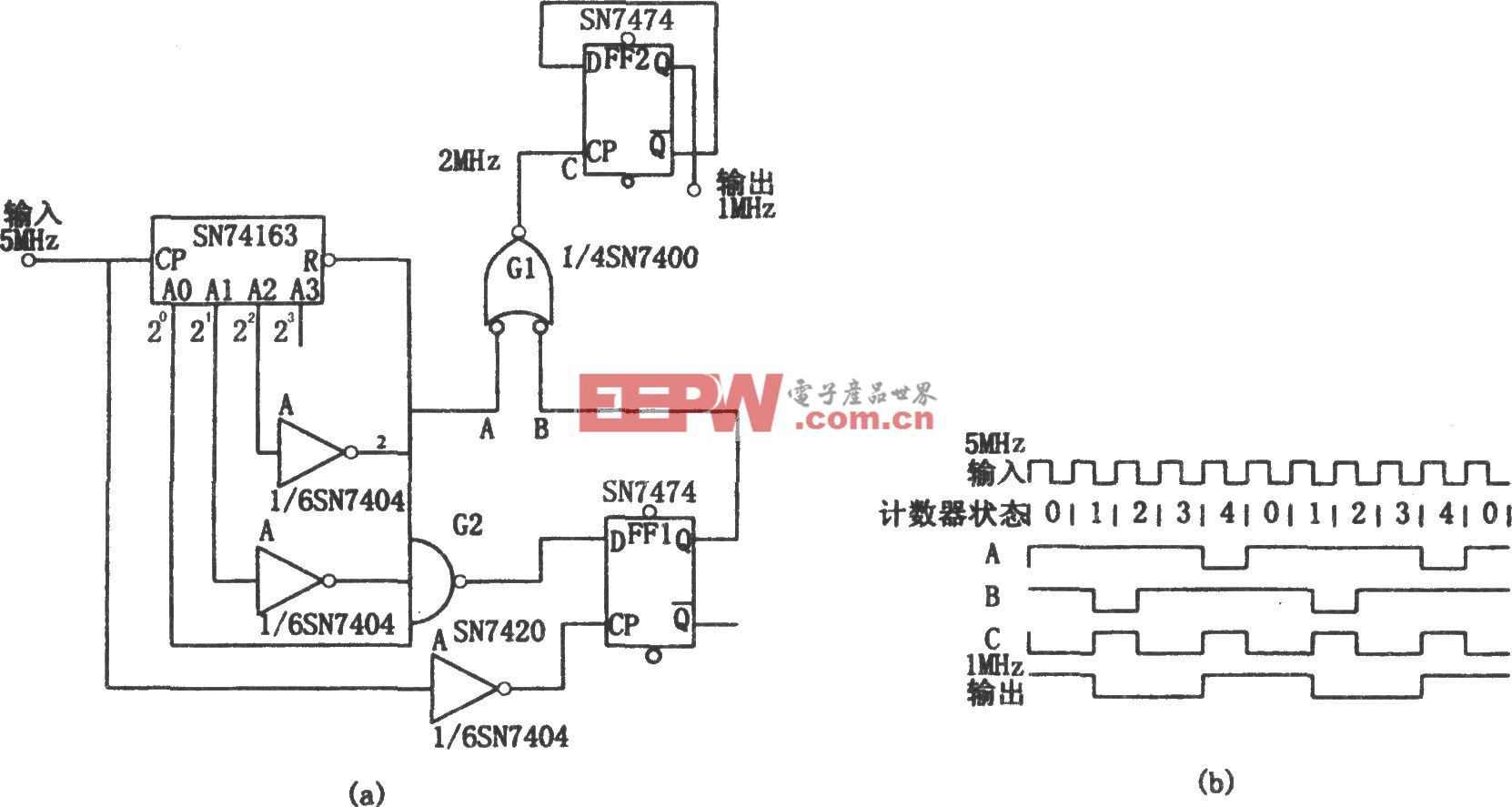

计数器按脉冲的作用方式可分为异步计数器和同步计数器;按计数过程中数字的增减可分为加法计数器、减法计数器和可逆计数器;按计数体制的不同,又可分为二进制计数器,十进制计数器和其他进制计数器。图Z1504为三位异步二进制计数器的逻辑电路。它由三个接成触发器的JK触发器组成,因此,每当有一个CP信号,触发器的状态就要翻转一次,而且,状态的翻转是发生在触发脉冲的下降沿。计数前,

上加一置0的负脉冲,使得Q3Q2Q1=000。第一个计数脉冲来到后,F1由0态变为1态,F2和F3的状态不变;第二个计数脉冲来到后,F1由1态变为0态,在它的Q端上产生一个负跳变的脉冲,致使F2由0态变为1态。可见,F1翻转两次,F2才翻转一次。同理,F2翻转二次,F3翻转一次。当第7个脉冲来到后,Q3Q2Q1=111;第8个脉冲来到后,Q3Q2Q1=000,且Q3向更高位输出一个负跳变的进位脉冲,此后,计数又进入新的计数周期。这种计数器的时序图和状态转换,分别如图Z1505和表Z1501所示。

评论