高性能∑-ΔADC-MAX1403的原理及应用

MAX1403是一种18位、过采样的ADC芯片,它利用∑-Δ调制器和数字滤流器可实现真正的16位转换精度。在应用中,为了得到高输出的数据速度,可选择数字滤波因子,并可降低转换分辨率。而调制器的采样频率可作为最小功耗和最高输出数据速率选择的首选条件。

MAX1403能够提供具有独立编程(增益从1V/V~+128V/V)的三路真差动输入通道,并能补偿输入参数电压的直流失调。而这三路真差动输入通道还能组成五路伪差动输入通道。另外,该芯片还具有两个附加的差动校正通道,它能对增益和失调误差进行校正。

MAX1403 能够对所有输入信号进行处理,并通过串行数字接口向外提供转换结果。当主机时钟频率为2.4576MHz或1.024MHz时,片内数字滤波器能够对线路频率和有关谐波频率进行处理,并使这些频率的幅值为零。以使在无需外接滤波器的条件下也能获得较好的滤波效果,同时,这也有助于提高输出端数字信号的质量。

MAX1403的主要特点如下:

●分辨率为18位;

●具有8个寄存器;

●功耗低

●具有两个匹配的传感器激励电流源;

●3个真差动输入或5个伪差动输入通道;

●2个附加输入校正通道;

●带有一个双向串行通讯接口;

●模拟电源和数字电源采用独立供电方式;

●可用软件控制增益和失调。

2 引脚功能

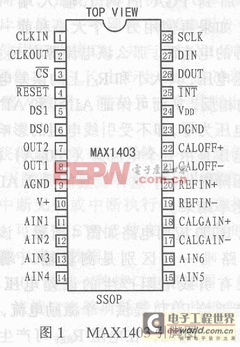

MAX1403芯片采用28引脚SSOP封装,它的引脚排列如图1所示。各引脚功能如下:

CLKIN:时钟输入引脚;

CLKOUT:时钟输出引脚。使用外部晶振时,将外部晶振连在CLKIN和CLKOUT之间;当使用外部其它时钟信号时,其时钟信号(频率为2.4576MHz或1.024MHz)在CLKIN输入,而CLKOUT不连。

评论