接地问题与回答

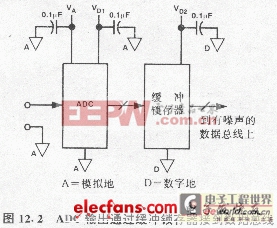

但是你说过的一件事使我大感忧虑。通常把ADC输出直接连到有噪声的数据总线上,是很 轻率的作法。总线噪声经过内部寄生电容耦合可能返回ADC模拟输入端。寄生电容从0?1到0 ?5 p F。如果把ADC输出直接连到靠近ADC的中间缓冲锁存器就要好得多(见图12?2)。缓冲锁存器 地线接到数字接地平面上,所以它的输出逻辑电平和系统其余部分的逻辑电平兼容。

答:假如新来的检查人员用一只欧姆表,看一看它们在封装体内部是否连在一起 。这种做法多半会被拒绝,因为集成电路可能会被烧。另外存在一个惯例,我们必须把这些 引脚做标记,以便指示它们的真实功能,而不是像我们想象的那样。

问:好!我不去做你刚才的试验了。现在讨论一个问题。我有一个同事,他设计了 一个模拟地和数字地独立的系统,他把模拟地引脚接到模拟接地平面,把数字地引脚 接到 数字接地平面上,他说系统工作得很好,怎么解释这件事?

答:首先,你按照未被推荐的方法去做,并不一定意味着你能一时侥幸成功,有 时你会陷入虚假的安全感(这就是鲜为人知的Murphy定律),有些ADC对于模拟地与数字 地 引脚 之间的外部噪声不敏感,你的同事偶然选到的可能就是这一种。如果要求我们对你的同事所 说的 “工作很好”的定义做考察,可能还会有其它的解释。然而ADC的制造厂家指出,在那种工 作条件下ADC的技术指标得不到保证。像ADC那样复杂器件要在所有工作条件下进行试验是不 现实的,特别是在不是首先推荐的那些条件下!你的同事这次是侥幸的。假如这个做法在将 来的系统设计中继续使用,你还是会相信Murphy定律最终会得到证实的。

问:关于ADC接地的基本原理现在我已经懂了,但对于DAC应该怎样接地呢 ?

答:应用同样的原则。DAC的模拟地引脚和数字地引脚连在一起并接到模拟接地平 面 上。如果DAC没有输入锁存器,应该把驱动DAC的寄存器的基准和接地引脚接到模拟地以预 防数字噪声耦合到模拟输出端。

问:对于含有ADC,DAC和DSP(例如ADSP?21msp50音频处理器)的混合处理 芯片应该怎样接地呢?

答:应用同样的原则。对于复杂的混合信号芯片,例如ADSP?21msp50,你决不能 把它仅看作是数字芯片!应该应用我们刚刚讨论的同样的原则。即使一个16位的Σ?ΔADC和 DAC的有效采样速率仅仅为8 ksps,转换器过采样工作频率仍然达到1 MHz。这种转换器需要 一 个13 MHz的外部时钟,而52 MHz的内部处理器时钟是由一个锁相环来产生的。正如你所看到 的,成功地应用这种器件需要懂得精密电路和高速电路的设计方法。

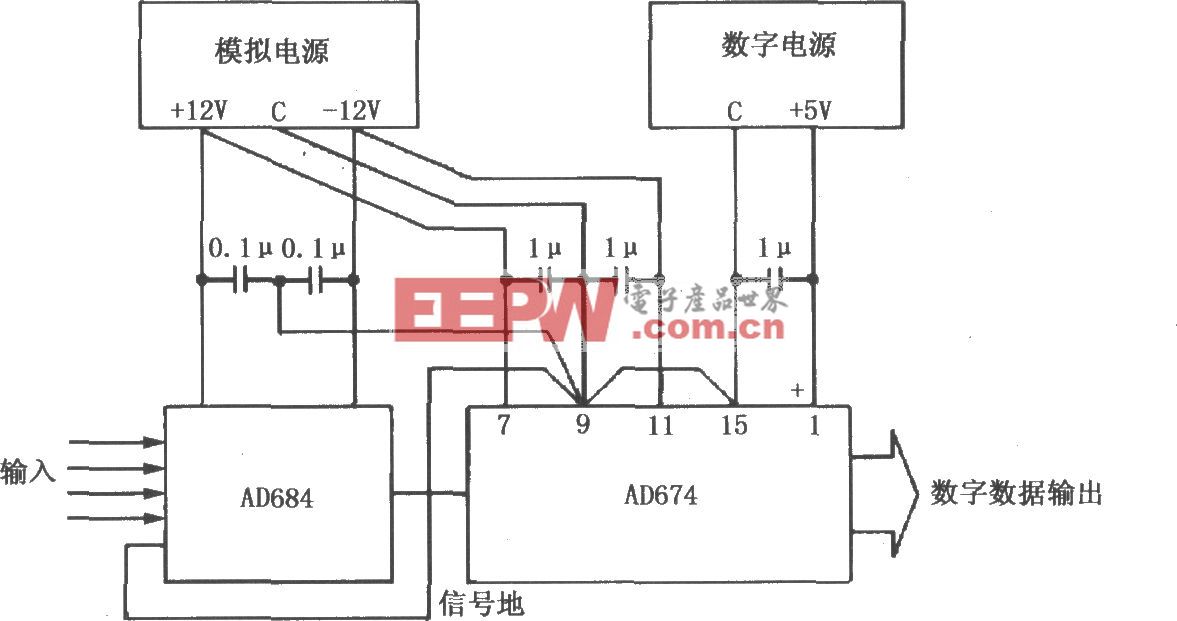

问:这些器件对模拟电源和数字电源要求怎么样?我究竟是买独立的模拟电源和数 字电源,还是买相同的电源?

答:这个问题实际上与数字电源的噪声大小有关。例如ADSP?21msp50有独立的+5 V 模拟电源引脚和+5 V数字电源引脚。

评论