USB 3.0应用的ESD保护设计

以上五项基本要求缺一不可,若有任何一项无法满足,则USB 3.0端口就无法被完善地保护。不过,同时符合以上五项要求的ESD保护组件其本身的设计难度相当高,若非具有丰富经验与扎实技术的设计团队将无法实现。

采用AZ1065的USB 3.0 应用ESD保护方案

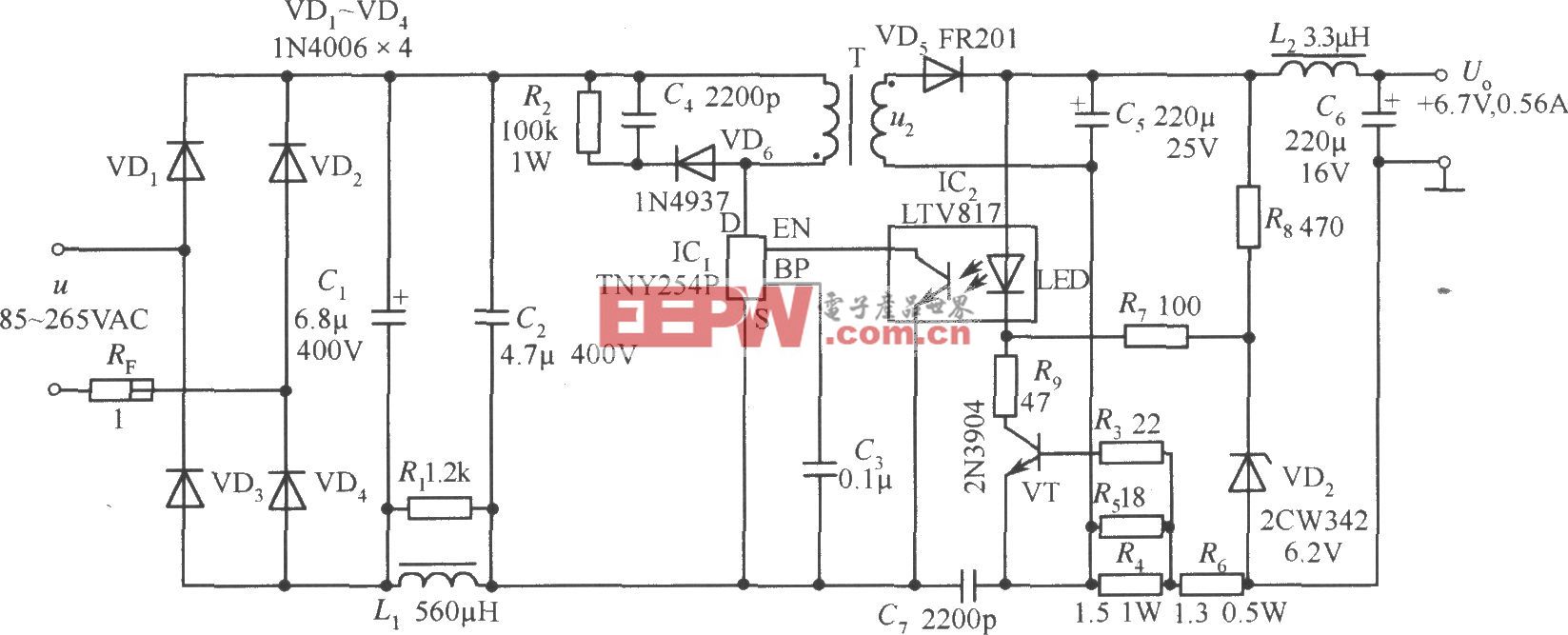

本文介绍的USB 3.0 应用的ESD保护方案,采用的是晶焱科技针对USB 3.0的保护需求推出的AZ1065系列ESD保护组件。为了将保护组件的寄生电容对4.8Gbps差动(Differential)信号高速传输的影响降至最低,AZ1065的寄生电容低于0.3pF。在极严格的电容要求下,任一引脚在室温时仍可承受IEC 61000-4-2接触模式10kV ESD的攻击。

最重要是,与相同的寄生电容相比,AZ1065拥有最低的ESD箝制电压,可有效防止数据传输时被ESD事件干扰,这样才能让具有USB 3.0连接端口的电子系统得以通过Class-A的IEC 61000-4-2系统级静电放电保护测试。利用传输线脉冲系统(TLP)测量AZ1065-06F后,可以观察到如图1所示的ESD箝制电压特性。

在IEC 61000-4-2接触模式6kV(TLP电流等效约为17A)的ESD攻击下,箝制电压仅有13.4V,足以有效避免系统产品在静电测试时发生数据错误、当机甚

评论