基于GAL的I2C总线时序模拟

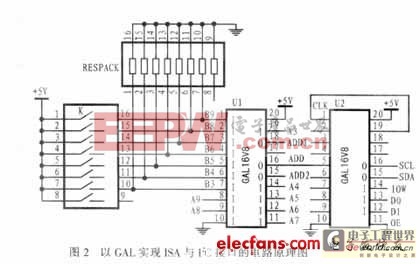

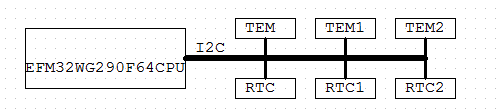

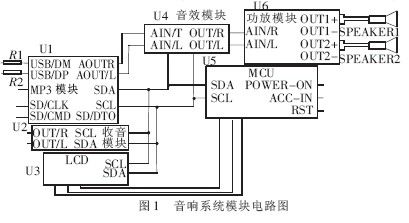

图2中,拨码开关K用以设定作为计算机外设的FI1256 MK2的地址,U1用于计算机访问外设时地址的译码,U2则用于实现用ISA总线的两条数据线模拟I2C总线时序。下面给出两片GAL的逻辑方程(以FAST-MAP格式书写),并对照方程简要说明电路所实现的功能。

通过以上方程可使U1完成地址的译码功能。当ISA总线上出现的外设地址与拨码开关设定的地址相匹配时,在其地址有效输出端ADDR上将得到高电平。由于GAL最多只能有8个或项,所以方程中使用了ADD1和ADD2两个中间运算结果,他们被当作反馈信号在GAL内部重新引到输入端。使用AEN信号是为了在DMA周期内屏蔽总线上出现的地址。

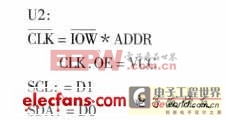

U2的时钟信号是由地址ADDR和外设写信号IOW的引入是为了消除总线上出现访问内存的信号,同时利用其上升沿锁存数据。SCL和SDA可分别用数据线D0和D1模拟。当一个外设写周期过后,D0和D1的数据将锁存在SDA和SCL上,而在下一个对相同外设地址的外设写周期到来之前是不变的。这就使得I2C总线的时序可以在D0和D1两根数据线上通过间隔输出数据的方式获得。

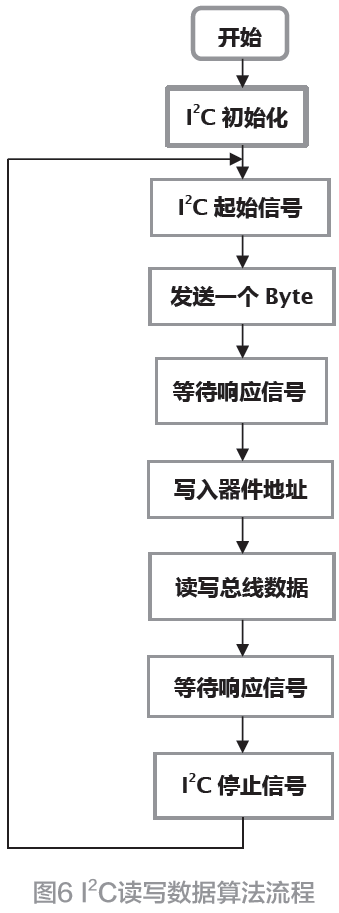

通过分析图1给出的数据传输格式,可以把传送的数据流划分为三种传送状态,即传送起始信号、传送终止信号和传送一个字节(后面带一个应答位)。不同的数据过程只是写入的数据字节数目不同。只要模拟软件能实现上述三种传送状态,就可以模拟出任何的主控器写操作过程。因此可以用下列子程序分别实现上述三种传送状态。

(1)字节传送子程序

由于SCL和SDA是用D1和D0模拟的,所以,只要往设定的I/O地址传送相应的数据就可以模拟传送不同的数据字节。为了保证数据的可靠传输,I2C总线规范对总线上的时序作了严格的规定。实验证明,ISA总线上信号的上升沿和下降沿都在10ns以内,完全可以满足I2C总线对上升沿与下降沿的要求,所以不需考虑信号的上升与下降时间,而只需考虑信号的建立和保持所需的时间即可。

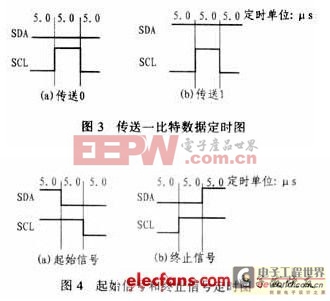

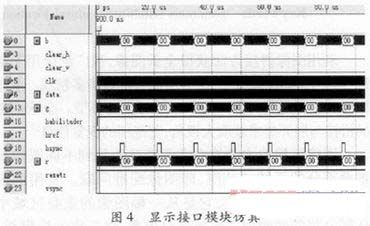

根据对I2C的定时要求,可以在SCL低电平的中点将信号进行分割,并把一个字节数据分为8个比特来分别进行传送(传送0和1分别用两个子程序实现),从而使SDA线上的数据变化总是处在SCL低电平的中点。图3所示是传送一比特数据的定时时序图。

由于在对FI1256 MK2的操作过程对实时性要求不是太高,所以可以使传送一比特数据的三个状态都持续5.0μs,这样,就可以满足所有的定时要求。把图3中的两个定时图进行组合即可传送任意的数据字节。在每个数据字节的8比特数据后,都会在SCL上送出一个时钟周期而让SDA保持高电平,以使FI1256 MK2送出应答信号。应答信号定时图与图3(a)相同。

评论