基于LM3478的50W DCDC升降压变换器设计方案

引言

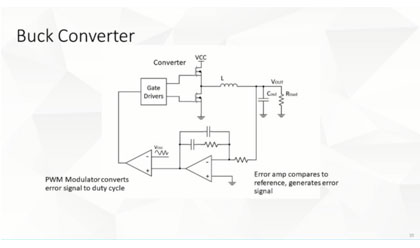

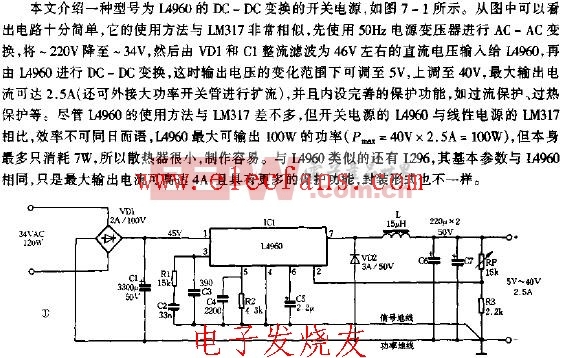

现代电子技术发展很快,半导体供应商不断推出新器件,从而推动电子应用工程师的不断创新设计,以满足市场的日益需求。本文介绍的即是基于客户的需求,应用美国国家半导体公司的新型电流型PWM芯片L

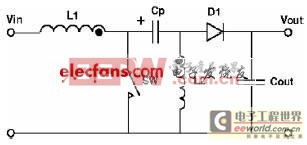

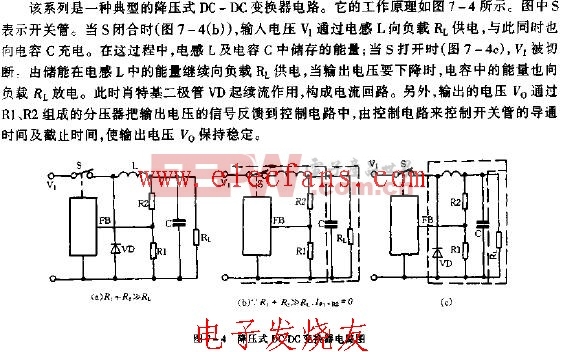

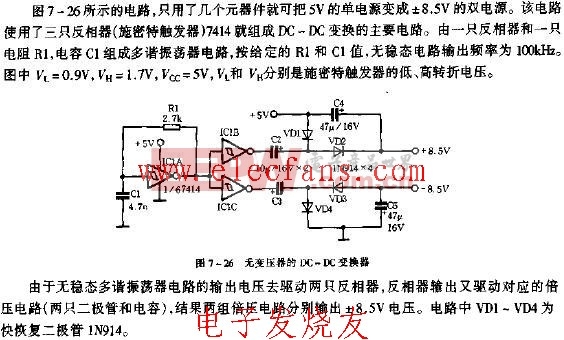

通常称之为升降压变换器SEPIC的简单原理如下:当SW开通时,加在L1,L2上的电压均为Vin,此时Cp并在L2上,且有Cp上的电压与L2上的相等。当SW关断时,L1中的电流继续沿着Cp、D1流向Cout输出到

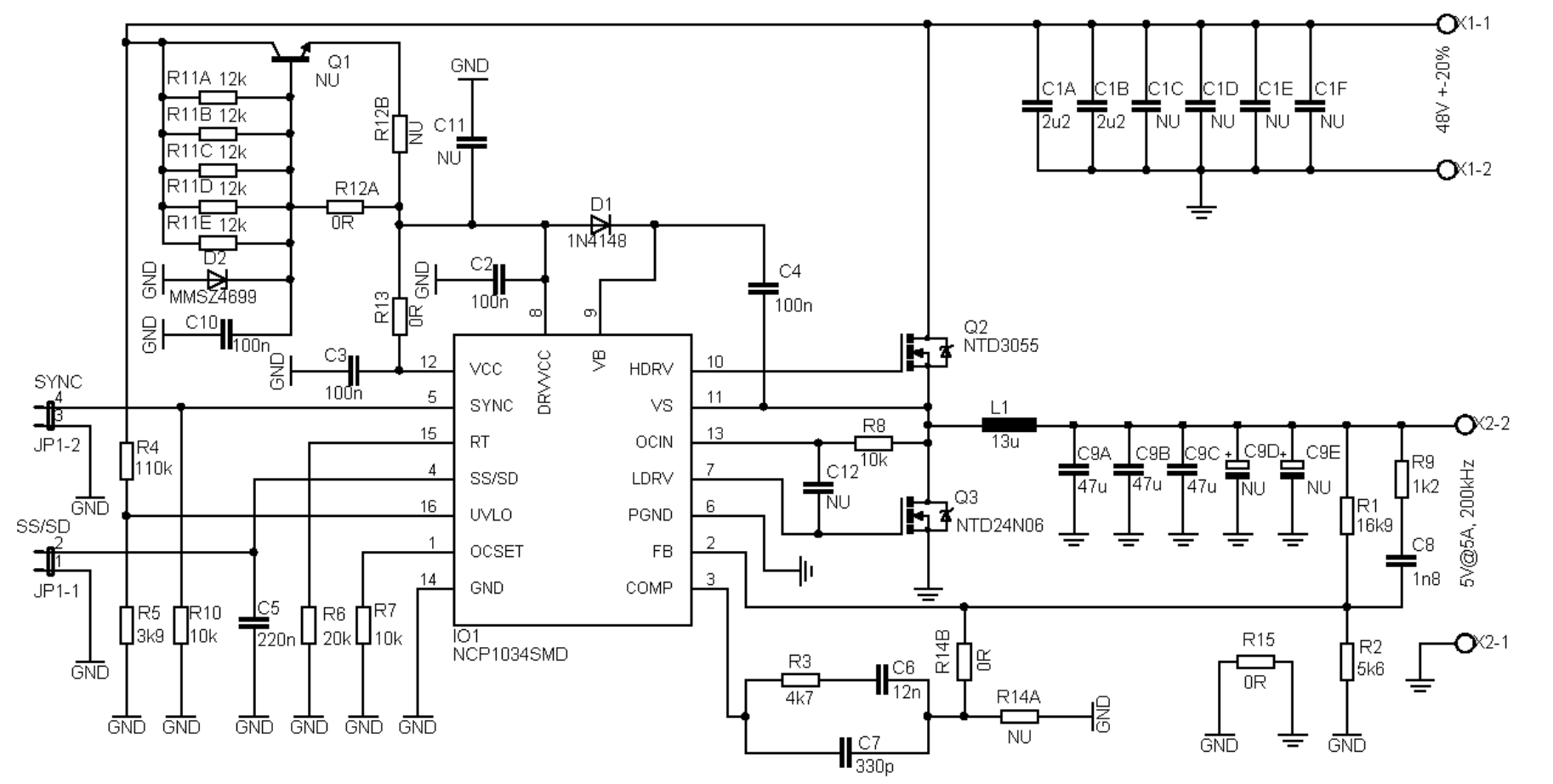

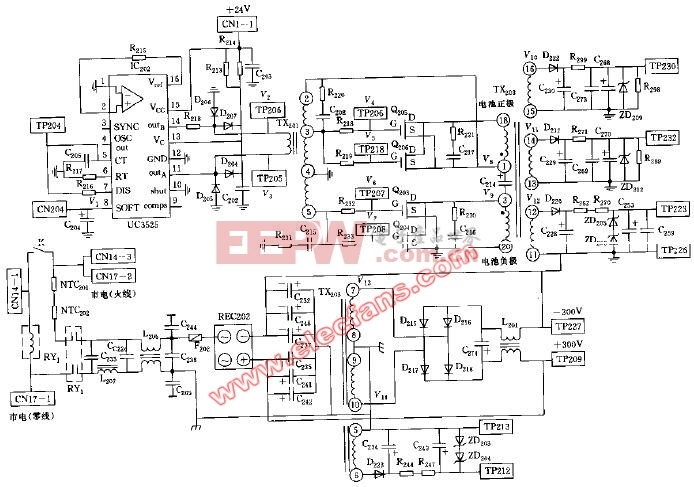

该电路是基于SEPIC拓扑、应用LM3478芯片按照客户的技术要求设计的。在该电路中,考虑到适配器的体积及储能电感磁性材料的体积,选定工作频率Fs=250KHz。

计算储能电感L3、L4的电感量及磁芯选择

首先由公式:D=Vout/(Vout+Vin)计算占空比。由于最严酷条件下的电感纹波电流是在最大输入电压下,所以D=12/(12+60)≈0.167。

计算储能电感l3、L4:正常情况下,L4的大小在确保最小负载电流下使电感电流连续,且输出纹波满足指标要求。为此,我们假定在20%最小负载电流下,允许有40%的峰-峰值纹波电流流过L4。

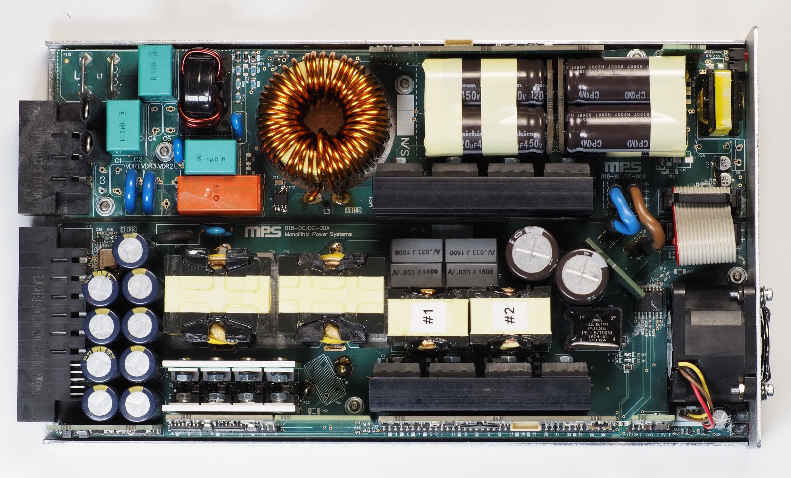

C1、C2为输入滤波,Q1、DZ1、DZ2、D1-1构成启动电源,L3、L4为储能电感,Q2为功率MOSFET,IC为PWM驱动芯片,R5为频率调整电阻,C3、C4、R2为反馈补偿,R3、R4为反馈分压电阻,R7为过电流取样电阻,C8、C9为SEPIC电容,R8、R9、C6、C7为吸收网络,D2为输出整流二极管,C10、C11、C12为输出滤波电容。当然要想符合EMC要求,输入端还应该有共模电感,差模电感,及X、Y等安规电容。

L=Vdt/di;

其中dt=1/FsD=1/(250103)0.167≈0.668,V为Vin在MOSFET开通时的值。因此,有如下计算:

L4=60(0.66810-6/0.4)=100.2μH。取100μH的标称值。由该SEPIC原理及设计经验可知,作为俩个分离的储能电感,L3的取值也为:100μH。

由于该电感为储能电感,因此,对磁性材料的选取要特别注意。此处选择的材料为:Magnetic公司的Kool Mu,相同性能的材料,其他公司又称铁硅铝。参数如下:

料号:77381-A7,黑色

尺寸:17.279.656.35(mm),为环型磁芯

评论