平衡电子设备静电防护和信号完整性设计

大多数的二极管厂商提供电流与电压的关系曲线图。虽然这些曲线图通常使用8/20 μs脉冲而非IEC 61000-4-2 准规定的脉冲,但是他们可用作电路阻抗的一般指标。对于8/20μs脉冲,电流和电压关系曲线完全是线性的,而且直线的斜率就是动态电阻值(Rdyn)。典型的ESD二极管动态电阻值(Rdyn)的变化范围从低于一个欧姆到三个欧姆。聚合体也有非常低的电阻。

另一方面,用于高速输入/输出端口的低电容抑制器具有很高的动态电阻,其变化范围是20欧姆或者更高值,这导致了被保护的ASIC电流值相对较高。事实上抑制器和变阻器从“被保护”的ASIC分流了很少的电流。因此上大部份的电流实际上传到了ASIC。显然,这一个特性使得他们很少被选用作ESD防护。

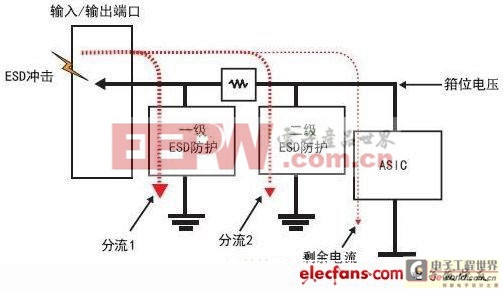

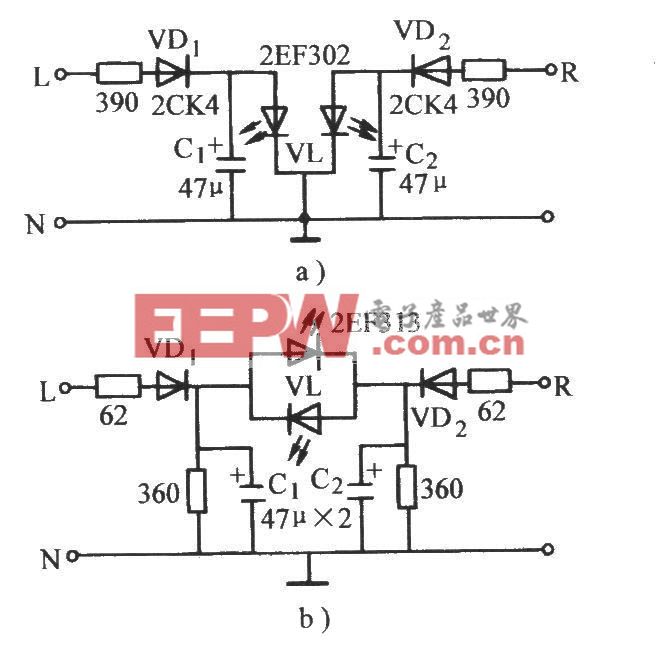

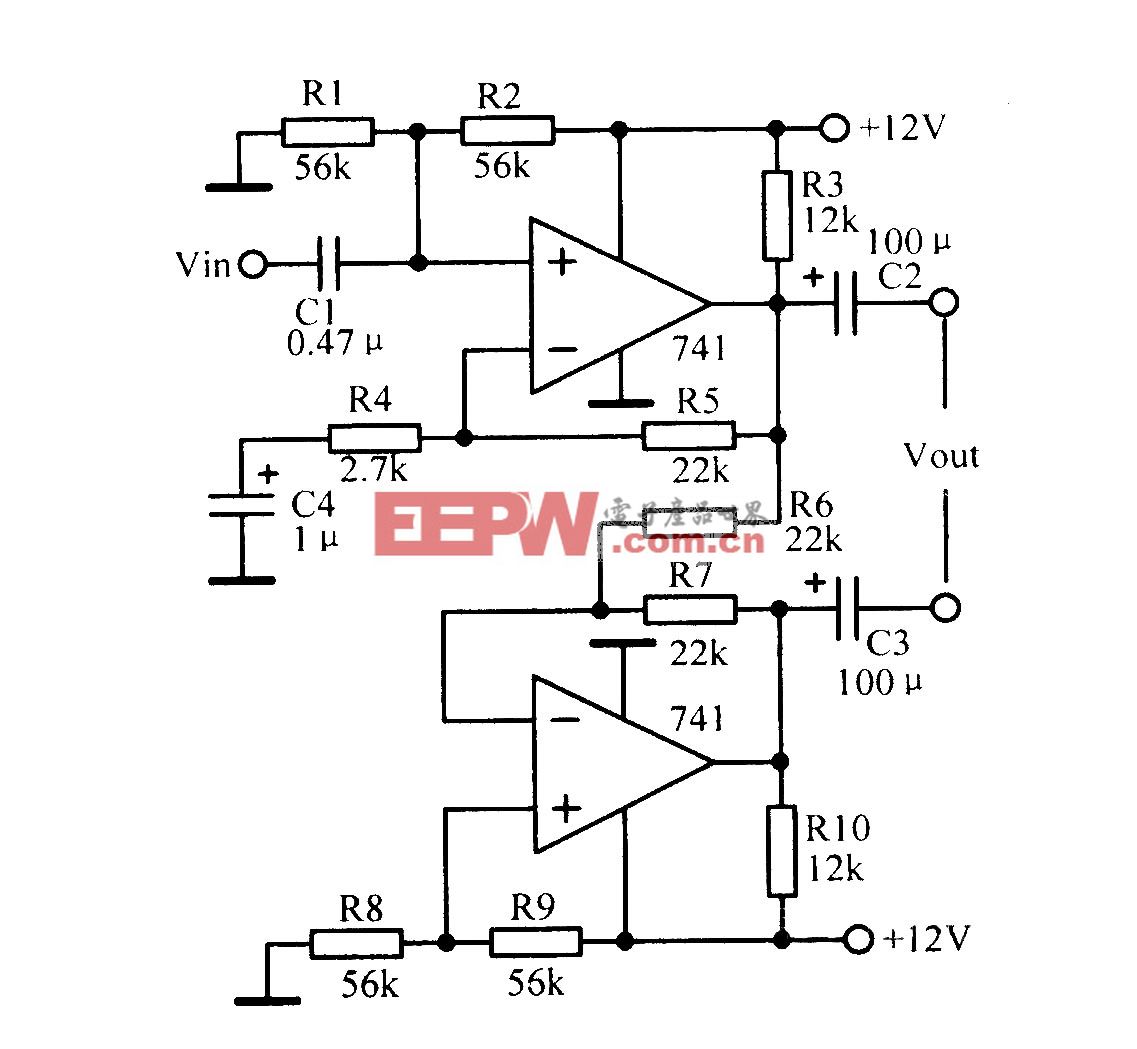

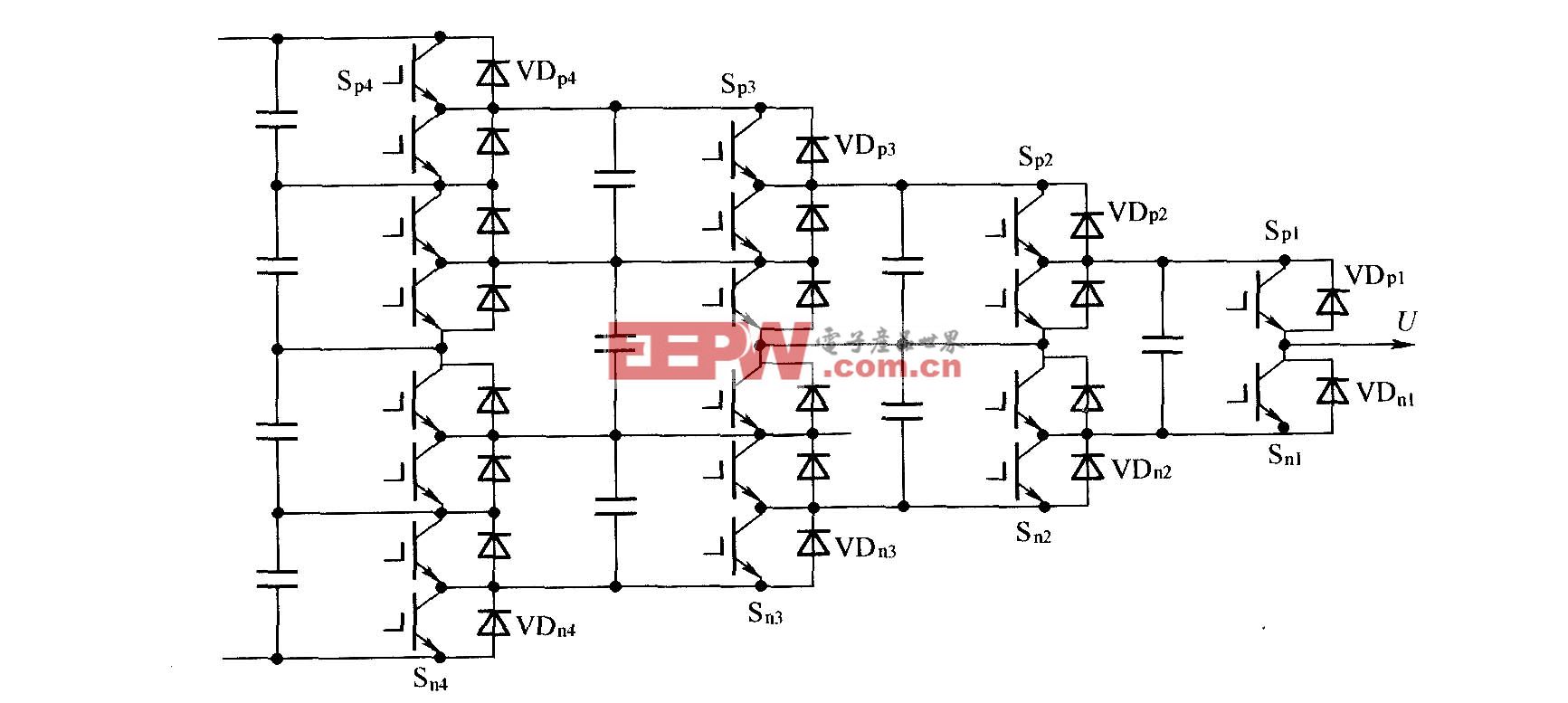

确保ESD防护的可靠性在传统的ESD防护技术中,虽然半导体二极管提供了最好的ESD保护,但它们不能够保护当前采用的亚微米几何尺寸制造的最新ASICs。通过采用传统手段进一步的减少这些装置的箝位电压和动态电阻则意味着增加电容量-这在高速应用中是个无法接受的取舍。一种新的ESD防护基本方法是利用新型双箝位结构,这种结构与电感、电阻一起集成了两级低电容二极管连同电感和一个电阻器,通过这种方式能在保持信号完整性的同时,显著地减少剩余电流、箝位电压并提供有效地ESD保护,如下图:

ESD防护电路图

当ESD冲击发生时,电路结构中的第一级开始抑制,分流大部份的电流并减小电压。剩余电流经过一个电阻后,冲击第二级电路,这将进一步减小电压,最终使流到ASIC的电流最小。

这种电路结构能为高速USB,高清多媒体和个人计算机设计提供ESD保护。通过片上匹配、减小偏差和EMI并改进由于集总电感引起的TDR(时域反射计效应),信号完整性得到改进。

评论