基于SoPC的实时视频处理与显示设计

当前基于软核处理器的图像系统已成为研究的热点,使用FPGA来构建基于片上可编程系统(SoPC)的图像处理系统,已成为一种趋势[1]。因此,本文采用SoPC技术,在Altera公司单片Cyclone系列FPGA上使用IP资源复用技术集成了NiosII软核处理器及各种输入输出接口,完成了对视频图像的采集、预处理、存储和显示几大功能。本系统对图像进行了灰度均衡化处理,使系统应用更广。由于直方图均衡能直接从已知的图像中提取信息,不需要额外的参数说明,所以在军用、航空、商业等领域,特别是红外图像增强领域[2]有实际的意义。SoPC是Altera公司提出来的一种灵活、高效的柔性设计,不需要修改硬件[3],就可方便地扩展和修改嵌入式视频采集功能。同时,由于融入众多的IP核,保证了设计的高效、快速。

1 系统总体结构及工作原理

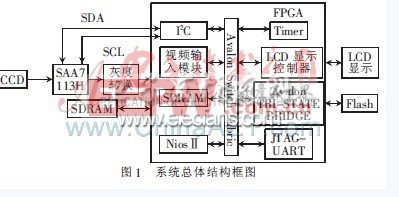

系统框图如图1所示。系统上电后,Nios II软核中的I2C控制总线对视频采集模块SAA7113H进行配置,FPGA依靠像素时钟和行、场信号同步采集SAA7113H芯片输出的视频信号中的灰度视频数据,把采集到的灰度数据进行灰度直方图统计和灰度分布均衡化处理。Nios II软核外部加一个延迟模块,与灰度转换模块输出的信号同步之后,视频输入模块开始工作,通过存储控制、DMA控制器传输视频信号,LCD显示控制等模块显示所采集的信号。所有处理都采用流水线操作,大大节省了系统的处理时间。

2 系统硬件设计

2.1 视频解码芯片SAA7113H初始化

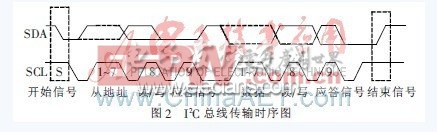

本系统中视频解码器的初始化配置由Nios II软核处理器通过I2C总线完成,主要包括对视频解码器的工作模式,输出行、场同步参考信号的时序关系以及输出数字信号的格式等进行设置。I2C总线是由Philips公司开发的一种两线制总线,由一条串行数据线SDA和一条串行时钟线SCL组成,可以实现数据通信,完成芯片配置。首先,I2C总线控制器发出一个数据传输的起始条件:SCL信号保持高电平、而SDA信号由高电平变为低电平时,开始传输地址数据流。起始条件满足后,发出一个8 bit的设备从地址,所有的外围设备开始响应起始条件并转换下一个8 bit寄存器地址(7 bit地址+1 bit读写位),由高位到低位依次传输。外围设备识别出传输地址后,在第9个时钟脉冲(确认位)把数据线变为低电平,然后开始将8 bit数据写入或者读出寄存器(读写位决定了数据的传输方向)。当时钟线SCLK为高电平、而数据线SDA由低电平变为高电平时,表示一次数据传输完成,停止I2C总线,等待下一次的传输开始。图2为I2C总线的数据传输时序图。

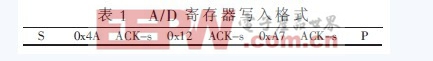

从SAA7113H的4个模拟输入端AI11、AI12、AI21、AI22输入的视频图像信号,经A/D转换后产生数字色度信号和亮度信号,分别进行亮度信号处理和色度信号处理。亮度信号处理的结果送到色度信号处理器,进行综合处理,产生YUV信号,经格式转化后从VPO(8位)输出。所有这些功能均是在I2C总线控制下完成。SAA7113的寄存器配置通过I2C总线来进行,遵从I2C总线协议。表1是SAA7113H寄存器的“写”操作格式。

其中,S为起始位,条件是SCL为高电平、SDA有下降沿、ACK-s为从动设备应答位,P为终止位。在初始化过程中要注意:SAA7113H的节点地址(Slave Address)上电、RTS0为高电平时,其I2C写地址为48H,读地址为49H;RTS0为低电平时,其I2C写地址为4AH,读地址为4BH。

评论