基于单片机的数字通信系统位同步提取的设计及分析

实现位同步的方法和载波同步类似,有直接法(自同步法)和插入导频法(外同步法)两种,而直接法又分为滤波法和锁相法。本文介绍的方法就是用直接法中的锁相环实现的。

1 数字锁相位同步提取原理

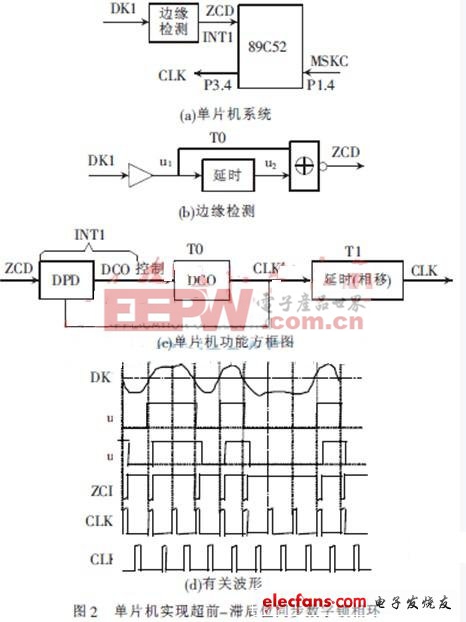

数字通信系统接收端位同步提取通常采用如图1所示的数字锁相环DPLL(Digital Phase Locked Loop)。DPLL包括3个部件:

(1)数字鉴相器DPD(Digital Phase Ditector)比较接收码元与本地DCO输出的位同步时钟相位,输出反映相位差的数字信号。

(2)数字环路滤波器DLF(Digital Loop Filter)对DPD输出相位误差数字信号滤波,去掉随机噪声的影响,输出较准确的相位误差数字信号。

(3)数控振荡器DCO(Digital Controlled Oscillator)是数字电路构成的振荡器,输出与接收码元相同速率的位同步时钟脉冲CLK,其相位受相位误差数字信号控制可提前或推迟,最后与接收码元相位锁定。

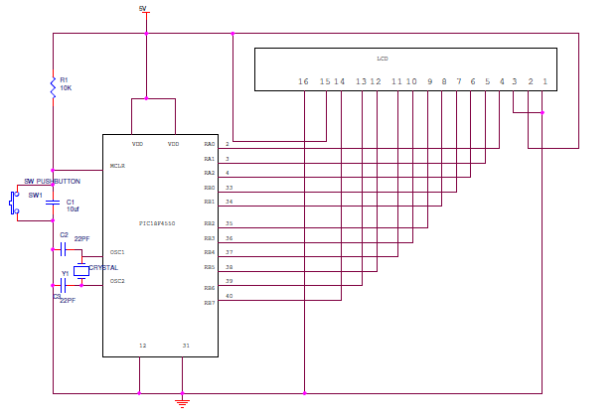

DPD及DCO是构成数字锁相环必不可少的部件,DLF可视需要而加入。3个部件各由多种形式的电路组成不同的数字锁相环。最典型的数字锁相环为超前-滞后型数字锁相环,又称为微分整流型数字锁相环,在码速率不高时可由图2所示单片机系统实现。图中,边缘检测又称为过零检测,它将输入数据信号DK1放大整形后,再将其跳变沿(整形前的过零点)变换为窄脉冲ZCD,送至单片机的外部中断输入端INT1。边缘检测中的延时电路可用几级门实现。微分整流电路与边缘检测电路具有相同功能。

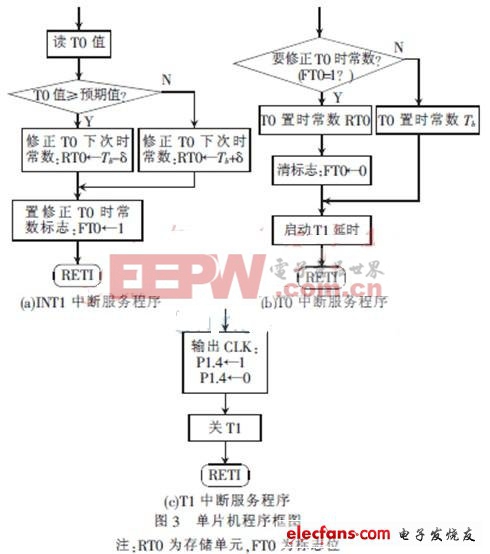

该数字锁相环未用DLF。单片机内T0定时器及其中断服务程序实现DCO功能。在DK1无跳变沿(无ZCD负脉冲)时,单片机不进入INT1中断服务程序,T0定时为输入码周期Tb。在DK1有跳变沿时,进入INT1中断服务程序,首先读取T0当前值与预期值(Tb/2时常数),通过比较确定DCO相位与DK1数据跳变沿相位关系是超前或滞后,据此调整DCO相位。若DCO相位超前,则设置T0下周定时为Tb+δ,使DCO相位推迟;若DCO相位滞后,则设置T0下周定时为Tb-δ,使DCO相位提前,最后实现DCO相位与DK1数据相位锁定。总之,INT1中断服务程序实现DPD及DCO控制功能,T0定时器及其中断服务程序实现DCO功能。T1定时器及其中断服务程序实现延时即相移,使最后输出的位同步时钟CLK与DK1(或DK2)的相位差为0或180°:当传输系统频带不受限、采用MSK/FSK调制解调方式时,DK1为方波,接收端采用积分/采样/判决进行检测,两者相位差应为0,即CLK与DK1数据边沿对齐;当传输系统频带受限、采用GMSK/GFSK调制解调方式时,DK2(DK1经LPF后的信号)为钟形脉冲,CLK应对准DK2码元中点采样/判决,两者相位差为180°或Tb/2,如图2(d)所示。T1延时由P1.4输入信号MSKC控制。INT1、T0及T1中断服务程序框图如图3所示,主程序完成3个中断源初化及其他初始化后就踏步。

位同步提取数字锁相环由CPU2实现,其P1.4输入的控制信号MSKC来自CPU1,由工作方式决定:在FSK/MSK工作方式时,MSKC=1;在GMSK/GFSK工作方式时,MSKC=0。

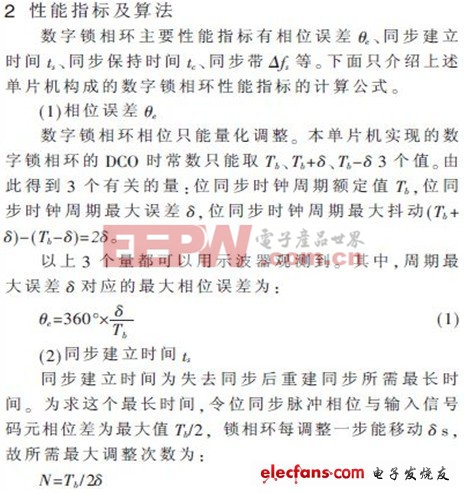

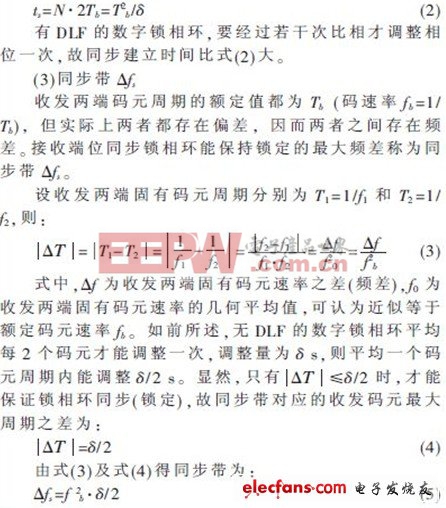

对接收的随机数字信号,可近似认为两相邻码元中出现00、01、10、11的概率相等,其中有数据跳变的占一半。而对无DLF的数字锁相环而言,每发生数据跳变可调整相位一次,因此平均每2Tb s可调整相位一次,故同步建立时间为:

有DLF的数字锁相环,调整相位的速率要比无DLF的低,故同步带比式(5)小。

由式(1)、式(2)、式(5)可知,3个性能指标都取决于DCO周期调整步距δ:δ愈大,同步带愈大,同步建立时间愈短,但相位误差却增大了。所以δ应折中选取,在保证锁相环路能锁定(同步)的前提下,δ尽可能取小些,以减小相位误差。

3 本设计采用单片机芯片实现数字电路相关器件,简化了相关器件复杂的逻辑电路设计,降低了系统的功耗和成本,提高了系统的可靠性。实现位同步的方法很多,本文讨论的是采用数字锁相环技术来提取位同步信号。在位同步提取中,如何缩小同步建立时间、降低位误差及增大同步保持时间是好的位同步设计的努力方向。

数字通信相关文章:数字通信原理

通信相关文章:通信原理

鉴相器相关文章:鉴相器原理 脉冲点火器相关文章:脉冲点火器原理 数字滤波器相关文章:数字滤波器原理 锁相环相关文章:锁相环原理

评论