DSP实现EAS扫频信号源设计(一)

4 硬件设计方案和软件实现

4.1 硬件设计方案

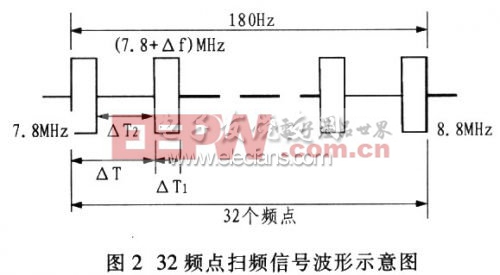

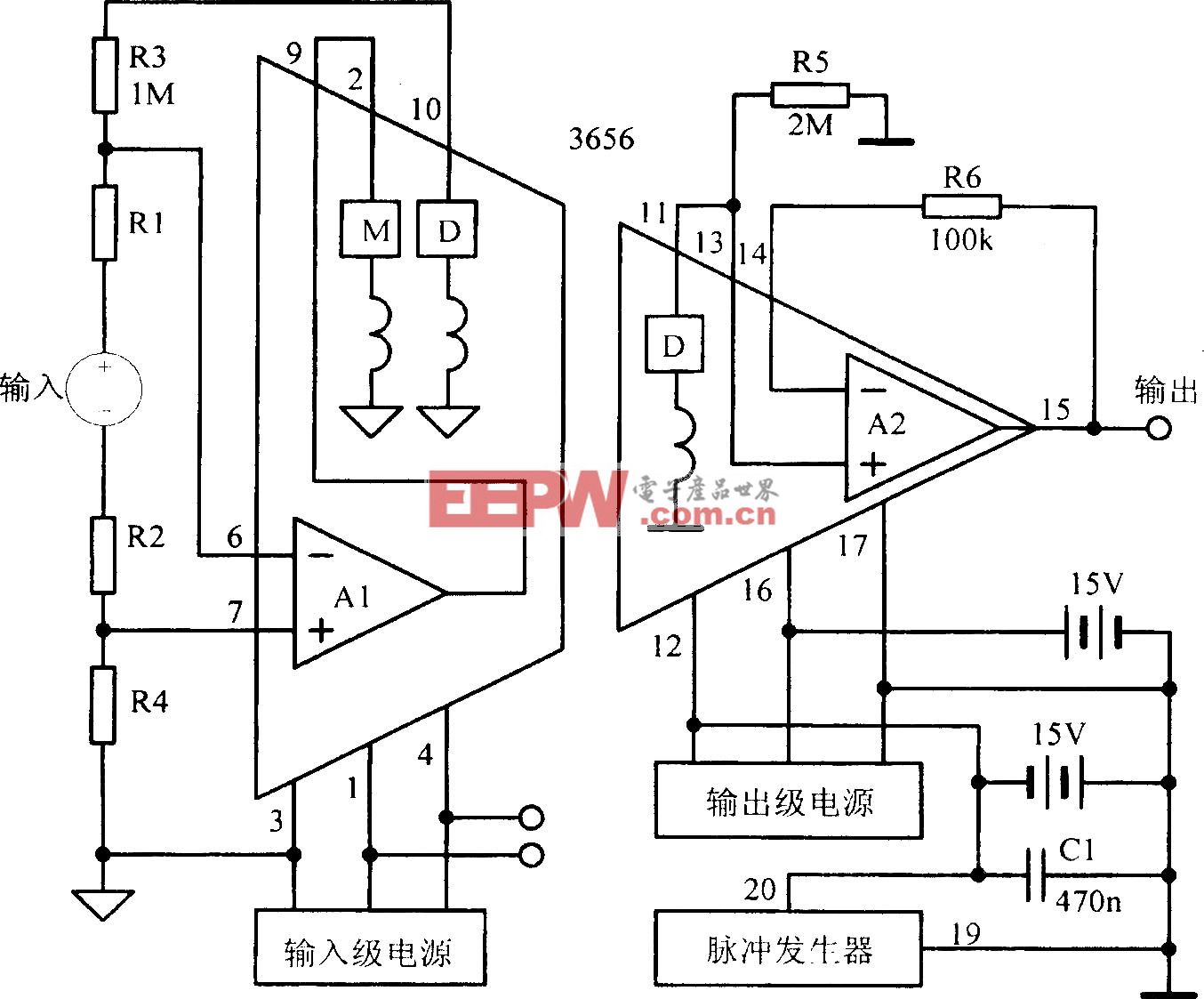

基于上述设计思想的硬件连接方案如图3所示,包括C5410、10MHz晶体振荡器、AD9834及滤波放大电路。由于AD9834的电源电压在2.3V到5.5V范围内可选,C5410的电源电压为3.3V。所以在连接时无需电平转换。10MHz晶体振荡器向C5410提供输入时钟。初始化C5410使其工作频率为100MHz,因为只有此时才能使其定时器周期寄存器从TOUT引脚输出50MHz时钟信号。该时钟信号输出到AD9834的MCLK脚,作为AD9834的工作时钟。理论分析指出:输出信号的相位噪声取决于时钟信号的相位噪声,在输出信号频率不变的情况下,输入时钟信号频率越高,相位噪声恶化越小。

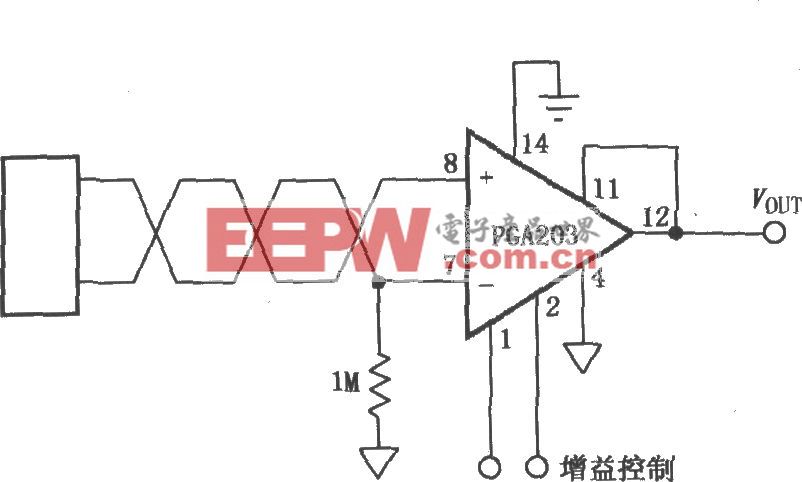

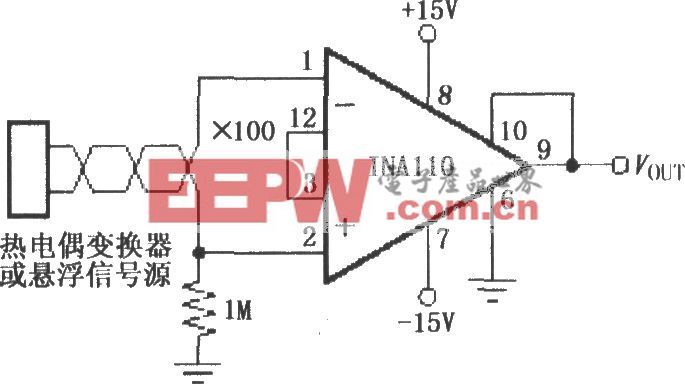

滤波放大电路对AD9834输出的扫频波信号进行进一步滤波处理和幅度放大,以滤除高频信号干扰和噪声,将信噪比控制在允许范围内。由于杂波信号干扰,从AD9834出来的扫频信号在没有滤波的情况下含有丰富的高频成分,采用RC或LC无源滤波电路处理后可以得到一组以8.2MHz为中心频率,扫频范围在7.7MHz~8.7MHz的较为清晰的扫频波。具体实现方案是先通过由1只去耦电容器和1只电阻器组成的RC回路滤掉由:DDS输出的扫频信号中的高频成分,然后使用带有电感器的复式滤波电路(可以选择LC滤波电路),经电感器滤波后不但负载电流及电压的脉动减小,而且波形也变得平滑,L、c的具体值可由f=1/(LC)1/2求得,其中f=8.7MHz,滤波电路如图4所示。由于AD9834的输出信号幅度最大只有O.8V,所以需将其幅值放大才能作为扫频信号源,在系统中可由1个高速运算放大器实现。

由于该电路是高速数,模混合电路,因此电磁兼容性能非常重要。特别是DSP和DDS共用1个电源,使得器件的工作信号通过电源线传输形成干扰。通常必须在电源接入处并人大容量的电解电容器和钽电容器,滤除低频噪声。还应该在每个器件的电源引脚处接1只0.01pF一0.1pF的去耦电容器。

评论