浅谈低电压低静态电流LDO的电路设计

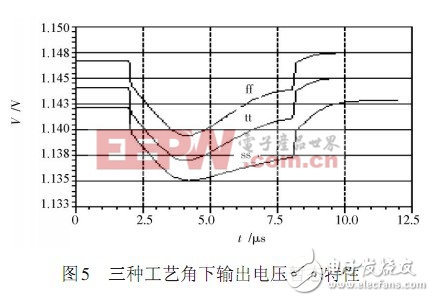

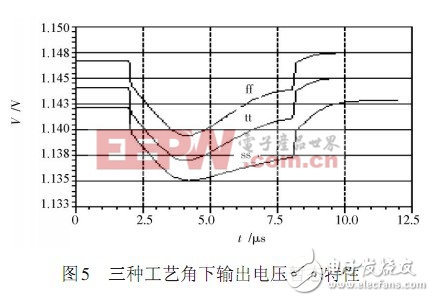

暂态输出电压变化如图5所示,当负载电流从0~30 mA瞬态变化时,输出电压变化最大仅为9 mV.

4 结语

本文给出了一种低电压1.14 V、低静态电流1.7 μA 的LDO,通过将带隙基准电压源与误差放大器合二为一获得精简结构的LDO.

因此实现了低静态电流消耗,同时获得较好的暂态输出电压性能,最大暂态电压变化仅为9 mV.

暂态输出电压变化如图5所示,当负载电流从0~30 mA瞬态变化时,输出电压变化最大仅为9 mV.

4 结语

本文给出了一种低电压1.14 V、低静态电流1.7 μA 的LDO,通过将带隙基准电压源与误差放大器合二为一获得精简结构的LDO.

因此实现了低静态电流消耗,同时获得较好的暂态输出电压性能,最大暂态电压变化仅为9 mV.

评论