意法爱立信移动平台多核处理技术(三)

近些年,为确保硅制造技术节点进一步降低,突破传统技术即将达到的极限,半导体企业进行了大量新技术研发,取得了很多具有突破性的开发成果,例如, FinFET 和 FD-SOI 制造工艺。

意法·爱立信将意法半导体的FD-SOI (全耗尽型绝缘体上硅)技术用于其性能非常优异的下一代28nm 移动平台。在这里,我们只从计算性能的角度简要分析FD-SOI 的技术优势,说明此项技术如何能够进一步提升单核处理器的性能,让我们继续专注速度更快的双核处理器,以获得更高的软件性能。

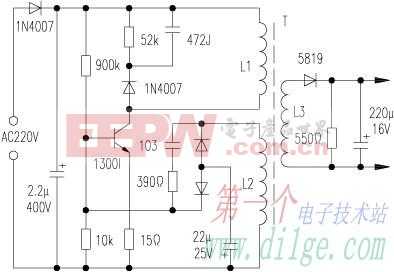

如图7 所示,由于插入超溥埋氧层衬底,FD-SOI 使晶体管电特性得到大幅提升,同时继续使用非常成熟的平面工艺制造芯片。

下面概括FD-SOI 的优点

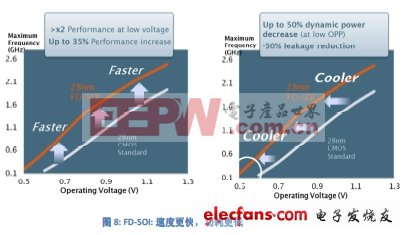

· 速度更快:在相同的技术节点,FD-SOI 晶体管的沟道比体效应晶体管的沟道短,而且前者是全耗尽型沟道,无掺杂剂。在这两个因素共同作用下,FD-SOI 晶体管在相同电压时开关速度更快,在功耗相同条件下,高压工作频率提高35%,低压工作频率提高。

· 功耗更低:有多个因素促使功耗降低:全耗尽沟道消除了漏极引起的寄生效应,在低功耗模式,可更好地限制载流子从源极流向漏极;更厚的栅电介质层可降低栅极泄漏电流;更好地控制体偏压技术 (为更好地控制速度和功耗而向晶体管体施加的电压)。结果,在高性能时,功耗降低 35%;在低性能时,功耗降幅更大,高达50% 。

· 工艺更简单:FD-SOI 制造工艺与28nm 体效应技术(bulk)的相近程度达到 90%,总工序减少15%,研发周期更短。此外,FD-SOI 技术无需压力源或其它类似的复杂技术,而其它工艺可能需要这些技术。最终工艺的复杂度低于体效应技术,远远低于技术。

从微处理器设计角度看, 相对于体效应技术,FD-SOI 的优势十分明显(见图

· 电压/功耗相同时,FD-SOI 可取得更高的频率,或者在频率相同时,FD-SOI 的功耗更低;

· 可取得的最高频率更高

· 采用FD-SOI 技术的处理器能够以更低的电压维持非常不错的频率 (比如,1GHz,0.65V),在低功耗模式时, FD-SOI 的对比优势更加突出,如图8 的低压区所示,在低功耗模式,的频率比bulk 技术高100%。

在高频率时,能效提高幅度大约35%。在大量的用例中,这个成绩足以让FD-SOI 双核处理器战胜速度较慢的bulk 四核处理器,如前文所述,这是因为目前软件性能提升受限。

在低功耗方面,FD-SOI 技术的影响更大,无需采用更复杂且还不成熟的异构多核处理器降低功耗的方式。

上文论述的扩展的工作模式是以前提到的FD-SOI 的技术优势共同实现的,其中体偏压(body biasing)扮演重要作用。体偏压是在晶体管体上施加特定电压,根据每个特定工作模式优调晶体管特性。FD-SOI 技术无需体效应晶体管的管体与源漏极之间的寄生二极管,所以,FD-SOI 准许施加电压范围更宽的偏压。

评论