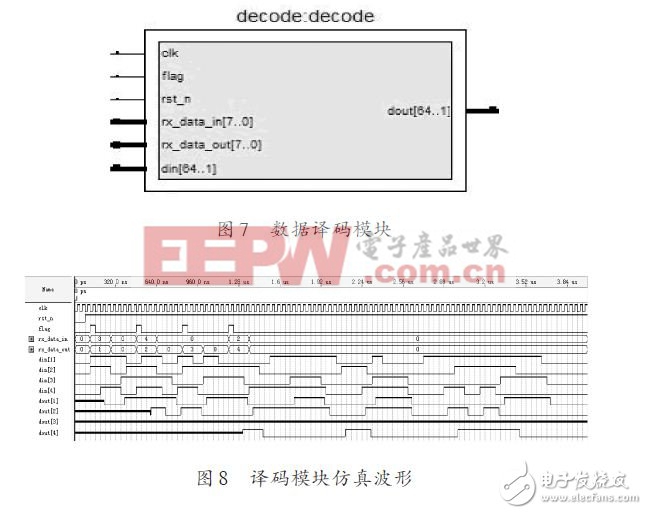

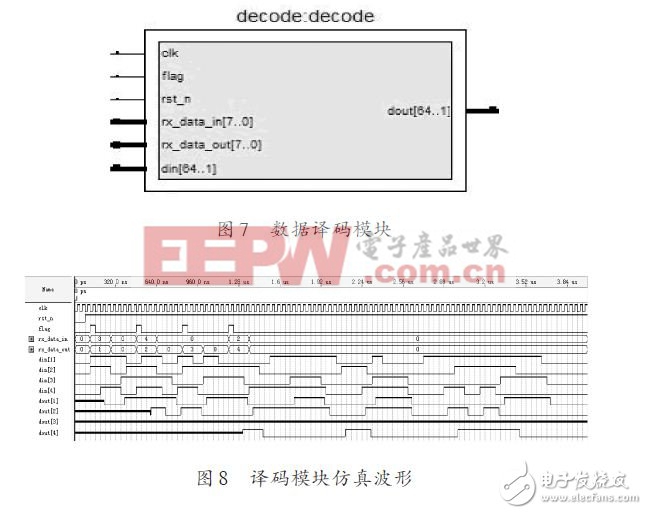

基于FPGA的基带64×64数据分配矩阵设计方案

4 结语

本文采用FPGA作为实现控制逻辑的核心部件,提出了基于FPGA的基带64×64 数据分配矩阵设计方案,并介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。经验证本系统基本能实现基带数字信号的分配路由,从而证实了该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

4 结语

本文采用FPGA作为实现控制逻辑的核心部件,提出了基于FPGA的基带64×64 数据分配矩阵设计方案,并介绍了上位机的软件设计思路和FPGA的内部编程实现及仿真。经验证本系统基本能实现基带数字信号的分配路由,从而证实了该方案具有规模大、成本低、高速等特点,可广泛应用于大规模基带数字系统测试及信号程控分配调度中。

评论