串行RapidIO交换器的应用优势

EMIF6? 是由 Texas Instruments 开发的一款专利接口,在业内应用多年,反响良好。但是,EMIF6? 现正用于从未尝试的 DSP 至 DSP 连接等应用。本文阐述了与以相同有效带宽运行的串行 RapidIO交换器相比,采用 FPGA 的八端口 EMIF6? 交换器具有的优缺点。

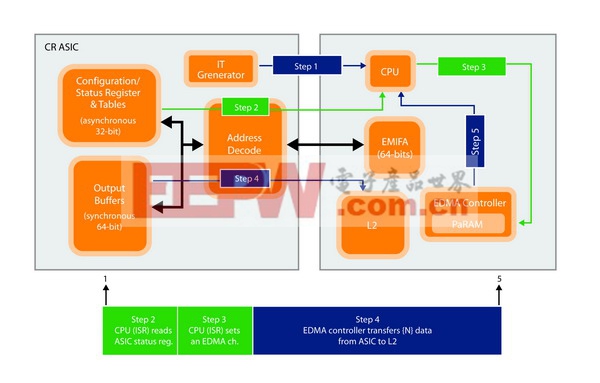

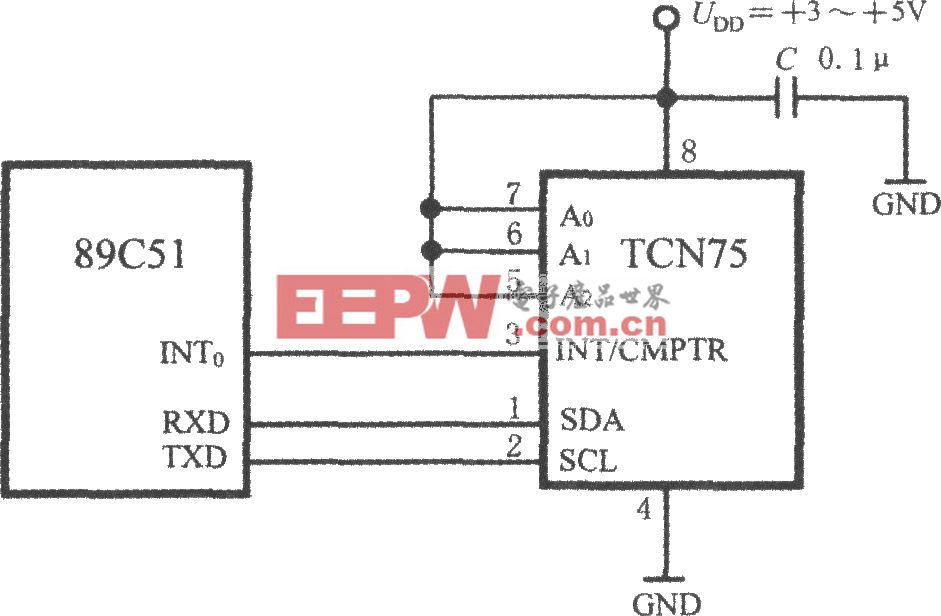

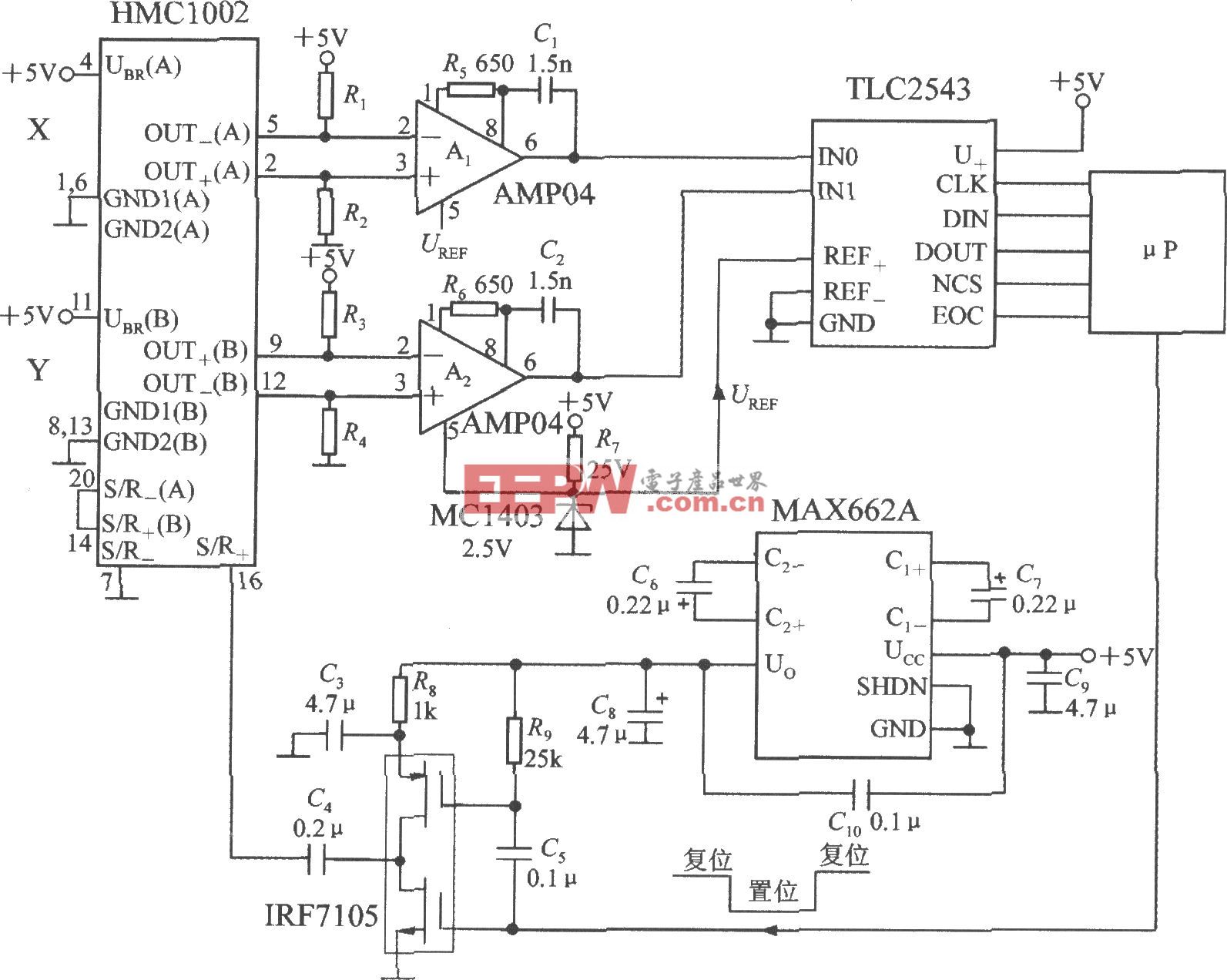

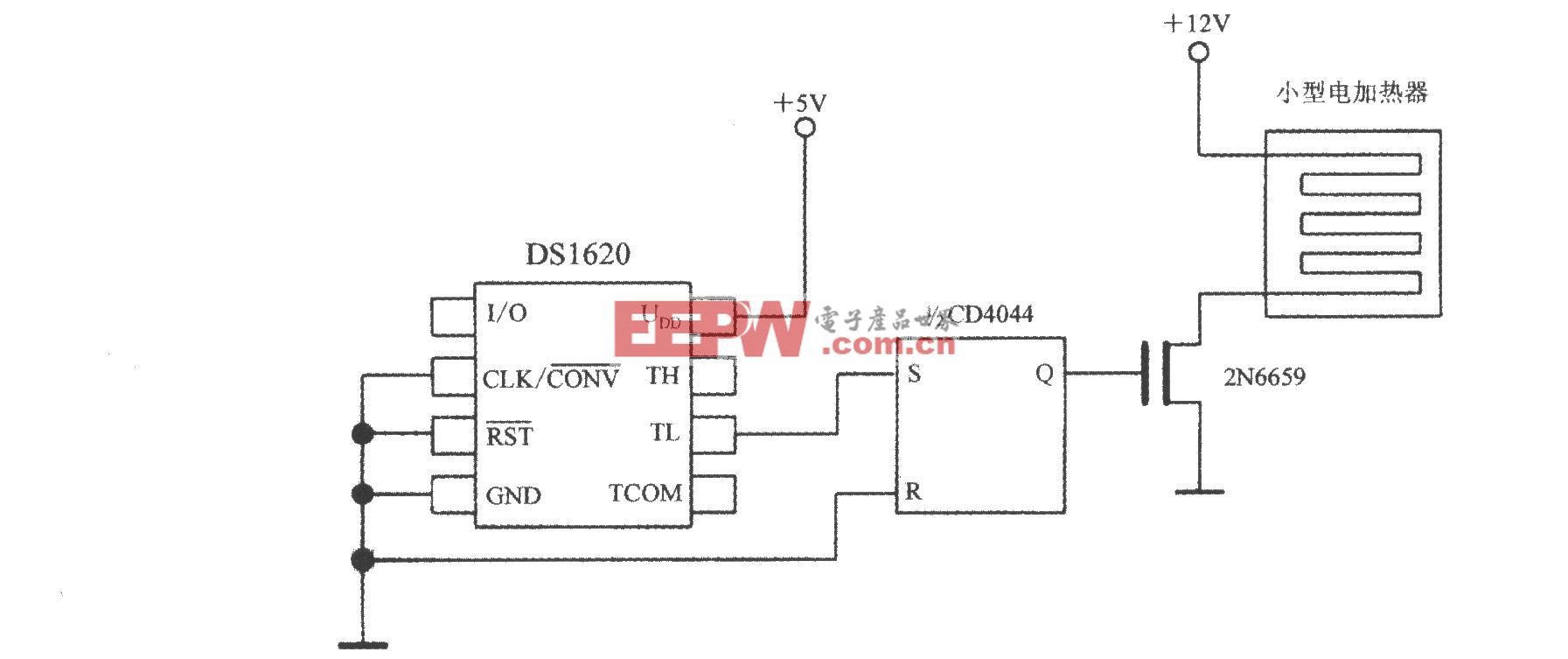

EMIF 标准是一种成熟、稳定的并行外部存储器接口,且已在许多应用中证明大有益处。但其能力仅限于主机,且需要昂贵的 CPU 中断服务程序,以便将系统内其他主机的数据传入设备。支持 EMIF 接口可能还需要庞大的软件开销(取决于数据传输的大小及频率)。图 1 所示的是传统的EMIF 应用示例,通过CPU 中断+ EDMA 方法从 CR ASIC 传至 DSP 的传输形式。

通过选择串行 RapidIO 等先进的系列接口,可实现诸多一般优点:

* 可配置性及性能 – RapidIO以 1.25、2.5 及 3.125Gb的速率支持每个链接,且可支持多达八个 4x链接或十六个 1x 链接。具有确定性及低延时的特点,且提供无阻塞交换矩阵架构。

* 控制 – RapidIO 具有可配置的 CPU 中断控制、支持错误管理及通过性能监控统计支持拥塞控制等特点。它还提供用于硬件错误恢复的 CRC 处理。

* 软件支持 – 纳入硬件终止端点从而实现较低的软件开支。另外,RapidIO 只要求低水平的配置及功能支持,同时提供高度抽象的信息传递 API。它还具有 CPU 开销无需由传输数据的大小决定(例如通过少量控制讯息)的优点。

|

|

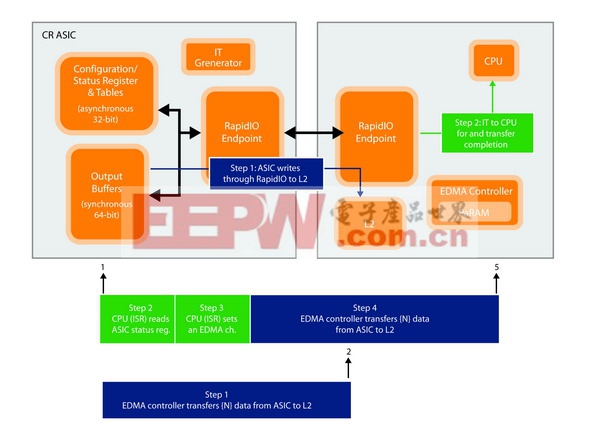

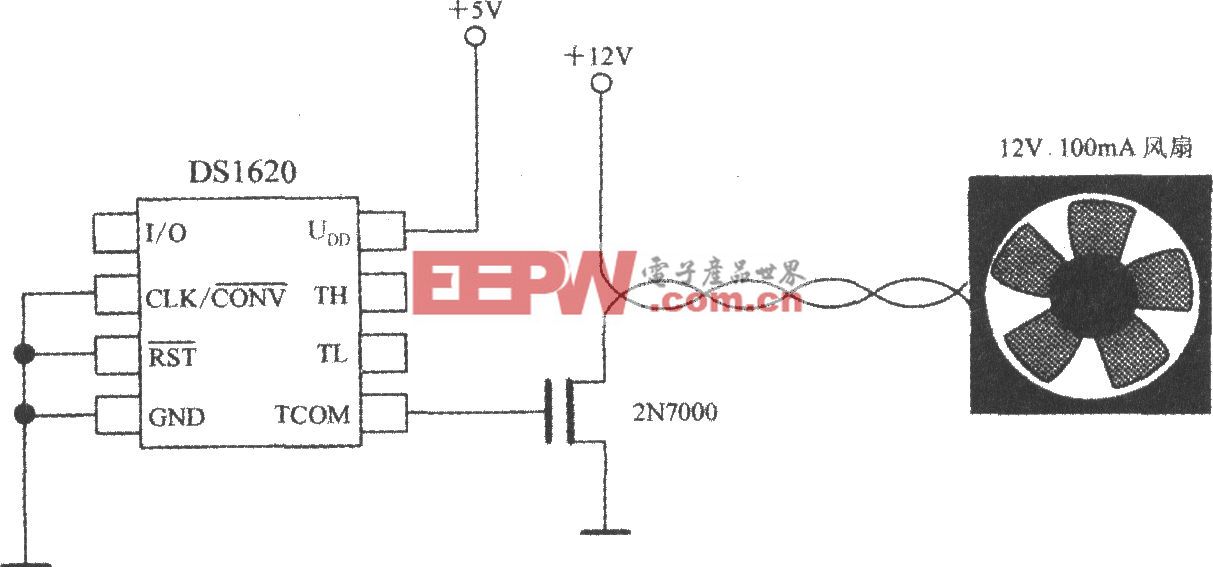

图2显示与图1相同的应用,而在实施时采用串行 RapidIO。采用此方法而不选择 EMIF6? 的具体优点可概述为以下几点:

* 灵活性 –EMIF6? 的局限性包括:它不是一个开放式标准接口,且其带宽限于 8Gb/s 半双工。另外,它并非可扩展的解决方案。相反,串行 RapidIO 具有开放式标准接口、带宽可扩展至高达 20Gb/s 及可扩展架构。

* 性能 – EMIF6? 属于损耗系统,不会存储和转发,也不会提供数据的优先次序。另外,通过交换器时还具有不可确定的延时。串行 RapidIO 是无损耗系统,可保证数据包传送具有四个优先次序等级。通过交换器时具有可确定的延时。

* 开发成本 – 当采用 EMIF6? 接口时,需要 FPGA 设计及确认资源。需承担的测试平台费用不可低估,且最后需要持续的产品支持。但是,采用串行 RapidIO,无需进行硅设计,且由于 EMIF6?的相对I/O 要求更高,因此执行本解决方案的成本较低。同时,PCB 的复杂性降低----单个 6? 位 EMIF 接口需要大约 97 只引脚,意味着八个端口的交换器只需要 776 只接口引脚----因此可降低成本。

* 其他优点 – 串行 RapidIO 提供 CRC 处理,可实现基于硬件的错误恢复,而EMIF6? 无错误检测/纠正。另外,后者不会提供状态或确认反馈,而串行 RapidIO 提供错误管理及报告功能。此外,较宽的并行接口比串行接口占用更多的 PCB 空间。

两种解决方案基本相同的一点是功率需求。使用相等的带宽配置时二者的端点功耗大致相同。当在6?位模式下以133MHz 工作频率运行时,EMIF 具有 8

评论