高速多模式RS编码的设计方案

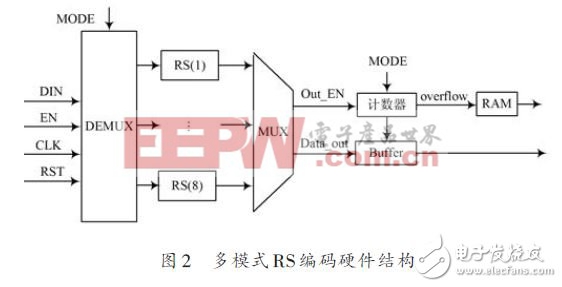

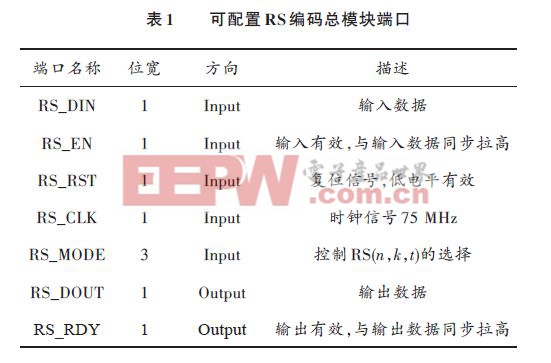

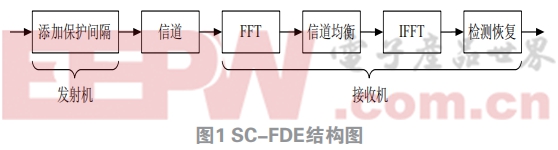

多模式RS 编码模块,根据MODE 信号对于可配置的RS 模块进行实时的配置。图2 为多模式RS 编码在L-DACS1 中硬件实现结构图,表1 为多模式RS 编码器模块端口说明。

根据协议规定,L-DACS1发射机使用归零卷积码,所以需要将RS编码器的输出数据末尾进行补零处理。因为卷积码的约束长度为6位,因此需要补6个零。

RS 编码后的数据放入缓存器中然后输出。根据MODE 信号对于计数器进行选择,计数器最大值时,将BUFFER 使能端置为低电平,同时激活ROM,顺序输出6个0值符号。然后计数器置为0,将BUFFER使能端拉至高电平。

3 多模式RS 编码器仿真

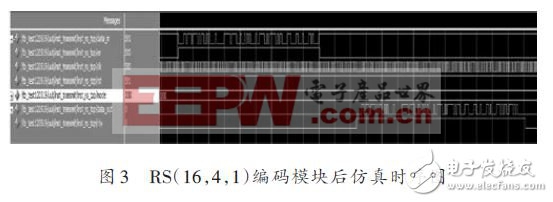

利用Verilog HDL 硬件描述语言对多模式RS 编码器进行仿真,对工程文件进行综合、布线和仿真,以RS(16,4,1)编码为例进行分析,其后仿真结果如图3所示。、

图3 中,MODE 是模式控制信号,可根据该信号来选择不同的RS编码模式。data_in为模块的输入数据,每次连续输入112 b数据;data_out为RS编码后输出数据,每次连续输出134 b;rdy 为数据输出有效标志位。

本次仿真RS(16,4,1)编码,模式信号MODE为000.仿真其他模式RS编码,改变MODE信号即可。

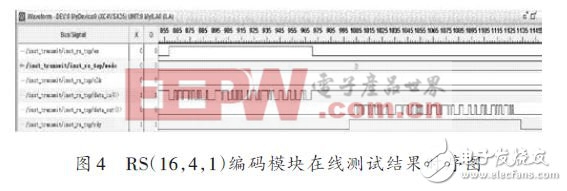

将仿真通过的工程文件使用ChipScope添加观察信号采样时钟、触发信号和待观察信号后重新综合、布局布线生成bit文件,下载到Xilinx公司的Virtex-5系列的XC5VLX110-F1153 型号的芯片后用ChipScope 进行在线测试,采用主时钟75 MHz,得到测试结果如图4所示。

图4中,en表示输入使能信号,data_in表示编码之前的数据,data_out表示RS编码后输出数据,rdy表示输出数据有效的信号,输入时钟频率为75 MHz,采样时钟频率为150 MHz.通过对比图3的仿真结果和图4的在线测试结果,可以验证在高速的时钟下设计的正确性。

4 结语

本文提出了一种基于L-DACS1系统中高速多模式RS 编码的设计方案。本方案先阐述了L-DACS1系统中多模式RS编码器的工作原理,利用FPGA设计实现了可以在高速多模式条件下正常工作的RS 编码器。同时用Verilog HDL 硬件描述语言对此设计进行了仿真验证,最后使用75 MHz的主时钟频率,在Xilinx 公司Virtex-5 系列XC5VLX110-F1153型号芯片下完成了硬件的调试,仿真及在线测试结果表明,达到了预期的设计要求,并用于实际项目中,以此证明该方案具有较强的实用性。

评论