TMS320VC5402 DSP与串行AD73360 A/D转换器的接口设

随着对信号处理要求的不断提高以及DSP技术的不断发展,越来越多的工程技术人员开始采用DSP进行系统设计。美国TI公司的TMS320VC5402(以下简称VC5402)DSP具有运算速度快、功耗小和性价比高的特点,已在个人移动通信、信号与信息处理以及自动控制等领域得到了广泛的应用。该芯片提供了两个多通道缓冲串行接口(McBSP)与外部设备进行通信。它与串行A/D变换器构成的信号采集与处理系统具有硬件设计简单、可靠性好的特点。本文将详细阐述VC5402与AD73360的接口设计。

1 VC5402的McBSP

VC5402的McBSP是一种同步串行接口,支持多种通信方式和SPI协议,该串口可以根据设计者的不同需求进行配置,使用非常灵活。它的主要特点如下:全双工的串行通信;连续的发送和接收数据流功能;具有外部时钟输入或内部可编程时钟两种时钟控制方式;可独立编程的发送和接收帧同步;多通道数据传输(最多可达128个通道);可选的数据宽度:8、12、16、20、24或32位;用于数据压缩的μ律和A律压缩扩展;可编程的时钟和帧同步极性。

McBSP包括6个引脚,分别是串行数据发送信号DX、串行数据接收信号DR、发送时钟信号CLKX、接收时钟信号CLKR、发送帧同步信号FSX和接收帧同步信号FSR。由于McBSP内带有一个可编程的采样和帧同步时钟产生器,所以串口接收、发送时钟和帧同步等信号既可由内部产生,也可以由外部输入。

VC5402的McBSP由23个寄存器进行控制,除了少数几个不能由程序访问之外,一般在串口进行数据通信之前都要对它们进行初始化,部分寄存器是存储器映射寄存器,必须通过子地址的方式进行访问。要访问McBSP的这些寄存器,首先要把所要访问的寄存器的子地址写到子地址寄存器SPSA中,然后才能对数据寄存器进行访问。

McBSP接收和发送数据的过程如下:在发送数据时,首先将要发送的数据写到DXR寄存器中,若XSR寄存器为空(说明上一次发送的数据已经由DX引脚送出),则将DXR寄存器中的数据拷贝到XSR寄存器中;然后在帧同步FSX和时钟CLKX的作用下,将XSR寄存器中的数据逐位移到DX引脚输出。在数据从DXR寄存器复制到XSR后,就可以将下一个要发送的数据写到DXR寄存器中,因而可以保证数据的连续发送。串口接收数据的过程与发送基本类似,但方向相反且VC5402的多通道串口的接收带三个缓冲器。

在VC5402片内,CPU与McBSP之间的数据传送有三种方式:查询方式、中断方式和DMA方式。每当串口接收到一个字(新接收的数据复制到DRR[1,2]寄存器中)或发送的字从DXR寄存器拷贝到XSR寄存器中时,都会改变串口控制寄存器1(SPCR1)中的RDDY和串口控制寄存器2(SPCR2)中的XRDY标志位,所以CPU可以通过不断查询的方法知道数据是否发送完毕以及是否接收到新的数据,从而决定下一步操作。CPU还可以通过串口的接收或发送中断事件,在中断服务程序中完成数据的传送,中断的触发事件是可以选择的,在进行处理之前必须预先设置好串口控制寄存器1(SPCR1)和串口控制寄存器2(SPCR2)中相应的位。第三种传数方式就是通过芯片的DMA与串口相连,由串口同步事件触发DMA完成数据的传送。

McBSP的初始化主要完成串口的配置,接收和发送可以分别设定,但要结合具体的硬件设计来进行。串口初始化的主要工作如下:设定FSR、FSX、CLKX和CLKR为输入还是输出以及它们的极性;设定是单相位还是双相位帧同步;设定每帧所包含的数据个数;设定传输数据的字宽(若为双相位帧同步,每一相位对应的字宽可设为不一样);设定第一个帧同步之后的帧同步是否被忽略;设定数据位的延迟;设定数据的符号扩展方式;设定所选择的传输通道;若采用内部产生时钟和帧同步信号,还需要对时钟和帧同步产生器进行设置。

2 串行A/D转换器AD73360

AD73360是AD公司推出的6通道模拟输入的16位串行可编程A/D转换器。由于采用Σ-Δ A/D转换原理,具有良好的内置抗混叠性能,所以对模拟前端滤波器的要求不高,用一阶RC低通滤波器就能满足要求。由于其采样率和输入信号增益都是可编程的,采样率可分别设置为64K、32K、16K和8K(输入时钟为16.384MHz时),增益可在0dB到38dB之间选择,因而它既适合于大信号的应用,也适合于小信号的应用。AD73360能保证6路模拟信号同时采样,且在变换过程中延迟很小。AD73360还能多片级联使用,从而扩充模拟输入的通道数。

AD73360有R-28和SU-44两种封装,图1是R-28封装的管脚图,下面仅对与McBSP接口设计有关的部分引脚进行说明。

RESET为AD73360硬件复位信号,用于对AD73360进行硬件复位;SE为串口使能信号,当SE为高电平时,AD73360正常工作,当SE为低电平时,AD73360被禁止,此时所有的输出为三态,所有的输入信号无效,同时AD73360进入节电状态。MCLK为外部时钟输入信号,通常由外部时钟驱动,MCLK进入AD73360之后,首先被分频产生DMCLK(内部主时钟信号),然后由DMCLK分频产生串口时钟信号SCLK,它们的分频因子都是可编程的;SCLK为串口时钟信号,通常作为DSP的同步串口的输入时钟信号;SDI和SDIFS为数据输入和输入帧同步信号,通常用于接收初始化控制字;SDO和SDOFS为数据输出和输出帧同步信号,通常用于输出转换的数据;其余的引脚分别为6路模拟输入、模拟电源和数字电源。AD73360有8个控制寄存器(CRA、CRB、CRC、CRD、CRE、CRF、CRG、CRH),在AD73360工作之前必须对这些寄存器进行初始化。AD73360有三种工作模式:编程模式、数据模式和混合模式。在编程模式下只接收控制字,输出无效的转换数据;在数据模式下,输入的控制字被忽略,输出有效的转换数据;在混合模式下,允许在数据转换过程中接收控制字。

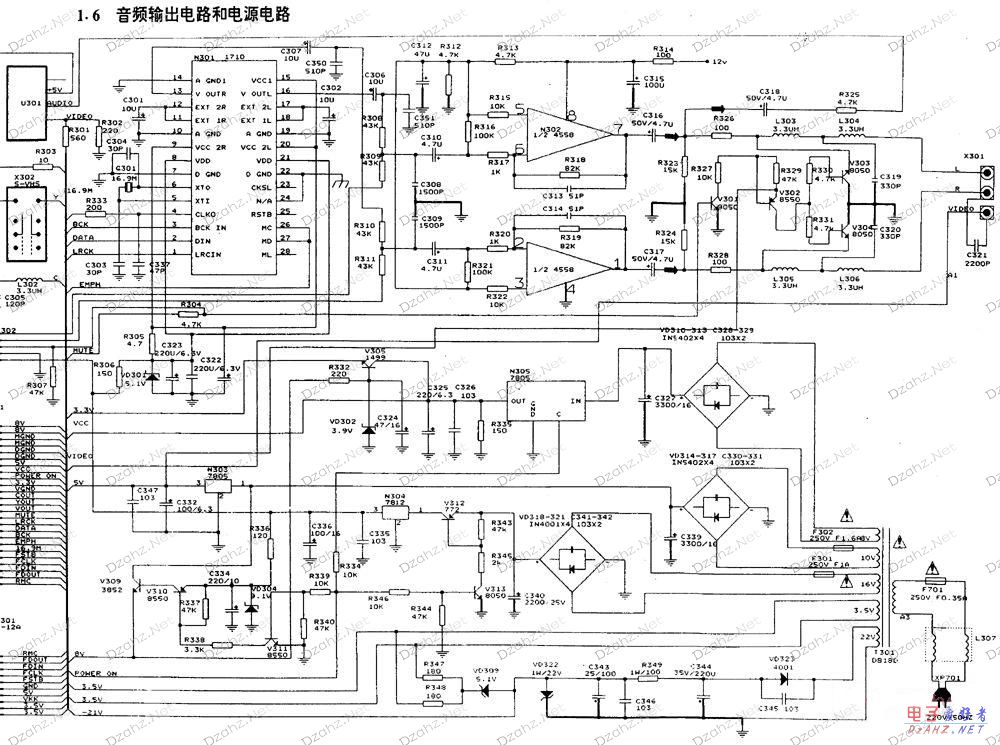

3 McBSP与AD73360接口的硬件设计

AD73360的模拟输入共有四种方式:直流耦合的差分输入、交流耦合的差分输入、直流耦合的单端输入和交流耦合的单端输入。交流耦合的差分输入的连接如图2所示,其中C1和C2起隔直作用,R1、C3和R2、C4分别为一阶低通滤波器,R3和R4的作用是把参考信号引入到输入端,C5为旁路电容。由于用到AD73360的内部参考源,所以初始化时必须使能参考信号(REFOUT)的输出。

McBSP(串口0)与AD73360的连接如图3所示。图中VC5402的McBSP的XF引脚与AD73360的SE引脚和RESET引脚相连,XF信号用于对AD73360进行控制;AD73360的串口时钟SCLK信号作为McBSP的发送信号(CLKX0)和接收时钟信号(CLKR0);McBSP的发送引脚(FSX0)、接收帧同步引脚(FSR0)与AD73360的输入引脚(SDIFS)、输出帧同步(SDOFS)连到一起,使McBSP的发送信号(FSX0)和接收帧同步时钟信号(FSR0)与AD73360的输出帧同步信号(SDOFS)保持同步。AD73360的数据输出引脚(SDO)和输入引脚(SDI)分别与McBSP的数据接收引脚(DR0)和数据发送引脚(DX0)相连。VC5402的定时器对主时钟分频,其输出再经过2分频得到AD73360的驱动时钟信号MCLK,实际上也可由晶振直接产生AD73360的驱动时钟信号MCLK。AD73360的最高输入时钟为16.384MHz,如果DSP主时钟为81.92MHz时,定时器分频因子可设为4。

4 McBSP与AD73360接口的软件设计

与硬件接口相对应的软件设计包括:设置定时器1的分频因子并启动定时器、McBSP的初始化、AD73360的初始化、开始接收并处理数据等。若AD73360的驱动时钟不是由VC5402分频得到,则第一步可以忽略。在串口初始化时,由图3可知,McBSP的发送、接收时钟和帧同步等信号都为输入,因而无需用到McBSP内部的采样和帧同步产生器;由于AD73360的控制字和转换的数据都为16位,所以McBSP应设置为单相位的接收和发送帧同步且传送每个字的宽度为16位。采用中断方式完成数据传送时,对McBSP各控制寄存器的初始化值如下:

RCR1=XCR1=0040h 每帧一个字,字宽为16位。

RCR2=XCR2=0001h 单相位帧同步,无压扩,第一个帧同步后的帧同步不忽略,一位数据延迟。

PCR=0h 发送和接收帧同步,时钟都由外部输入,发送和接收帧同步为高有效,发送和接收数据在

上升沿采样。

MCR1=1h 所有的接收通道被禁止,所需要的通道由RP(A/B)BLK和RCER(A/B)选择。

MCR2=1h 所有的发送通道被禁止且被屏蔽,所需要的通道由XP(A/B)BLK和XCER(A/B)选择。

RCERA=1h,RCERB=0h 仅打开接收通道0,关闭其它通道。

XCERA=1h,XCERB=0h 仅打开发送通道0,关闭其它通道。

SPCR1=1h使能串口接收,接收中断由RRDY标志触发。

SPCR2=0103h 使能串口发送,发送中断由XRDY标志触发。

McBSP(串口0)的初始化程序(SPSA为子地址寄存器,映射地址为38h;SPDATA为数据寄存器,映射地址为39h)如下:

stm #0000h,SPSA ;子地址寄存器指向串口控制寄存器1(SPCR1)

stm #0000h,SPDATA ;关闭串口接收

stm #0001h,SPSA ;子地址寄存器指向串口控制寄存器2(SPCR2)

stm #0102h,SPDATA ;关闭串口发送

stm #0002h,SPSA ;子地址寄存器指向接收控制寄存器1(RCR1)

stm #0040h,SPDATA

stm #0003h,SPSA ;子地址寄存器指向接收控制寄存器2(RCR2)

stm #0001h,SPDATA

stm #0004h,SPSA ;子地址寄存器指向发送控制寄存器1(XCR1)

stm #0040h,SPDATA

stm #0005h,SPSA ;子地址寄存器指向发送控制寄存器2(XCR2)

stm #0001h,SPDATA

stm #000eh,SPSA ;子地址寄存器指向管脚控制寄存器(PCR)

stm #0000h,SPDATA

stm #0008h,SPSA ;子地址寄存器指向多通道控制寄存器1(MCR1)

stm #0001h,SPDATA

stm #0009h,SPSA ;子地址寄存器指向多通道控制寄存器2(MCR2)

stm #0001h,SPDATA

stm #000ah,SPSA ;子地址寄存器指向接收通道使能寄存器A(RCERA)

stm #0001h,SPDATA

stm #000bh,SPSA ;子地址寄存器指向接收通道使能寄存器B(RCERB)

stm #0000h,SPDATA

stm #000ch,SPSA ;子地址寄存器指向发送通道使能寄存器A(XCERA)

stm #0001h,SPDATA

stm #000dh,SPSA ;子地址寄存器指向发送通道使能寄存器B(XCERB)

stm #0000h,SPDATA

stm #0000h,SPSA ;子地址寄存器指向串口控制寄存器1(SPCR1)

stm #0001h,SPDATA ;使能串口接收

stm #0001h,SPSA ;子地址寄存器指向串口控制寄存器2(SPCR2)

stm #0103h,SPDATA ;使能串口发送

McBSP初始化完成并使能McBSP后就可以通过它对AD73360进行初始化,其程序(DXR10和DRR10分别为串口0的发送和接收寄存器,映射地址分别为22h和20h)如下:

errorcrb: stm #8105h,DXR10 ;向CRB写控制字05h,DMCLK

ld DRR10,a =MCLK,SCLK=DMCLK/4,

stl a,ar1 采样率=DMCLK/1024

stm #0b905h,ar0

cmpr 0,ar1

bc errorcrb,ntc ;判断控制字是否已正确写入,

errorcrc: stm #8241h,DXR10 向CRC写控制字41h,使能

ld DRR10,a 参考电平输出,全局上电

stl a,ar1

stm #0ba41h,ar0

cmpr 0,ar1

bc errorcrc,ntc ;判断控制字是否已正确写入,

errorcrd: stm #8388h,DXR10 向CRD写控制字88h,通道

ld DRR10,a 1和通道2加电,增益为0dB

stl a,ar1

stm #0bb88h,ar0

cmpr 0,ar1

bc errorcrd,ntc ;判断控制字是否已正确写入,

errorcre: stm #8488h,DXR10 向CRE写控制字88h,通道

ld DRR10,a 3和通道4加电,增益为0dB

stl a,ar1

stm #0bc88h,ar0

cmpr 0,ar1

bc errorcre,ntc ;判断控制字是否已正确写入,

errorcrf: stm #8588h,DXR10 向CRF写控制字88h,通道

ld DRR10,a 5和通道6加电,增益为0dB

stl a,ar1

stm #0bd88h,ar0

cmpr 0,ar1

bc errorcrf,ntc ;判断控制字是否已正确写入,

errorcrg:stm #8600h,DXR10 ;向CRG写控制字00h,设置

ld DRR10,a 1至6通道为差动输入方式

stl a,ar1

stm #0be00h,ar0

cmpr 0,ar1

bc errorcrg,ntc ;判断控制字是否已正确写入,

errorcrh:stm #8700h,DXR10 ;向CRH写控制字00h,设置

ld DRR10,a 1至6通道为同相输入方式

stl a,ar1

stm #0bf00h,ar0

cmpr 0,ar1

bc errorcrh,ntc ;判断控制字是否已正确写入,

stm #8001h,DXR10 向CRA写控制字01h,使

rpt #400 AD73360进入数据模式

nop

AD73360初始化完成之后就可以打开串口的接收中断,在中断服务程序中接收A/D转换的数据。在该配置条件下,若输入时钟为8.192MHz,则AD73360为六路模拟采样,采样率为8kHz。图4为其中一路采样信号在CCS环境中的显示。

实践表明,由VC5402的McBSP和AD73360构成的信号采集和处理系统具有设计简便、结构紧凑、工作稳定和可以方便地在几种采样率之间选择等优点。与并行接口相比,采用串行接口的硬件连接线大为减少,这样不仅可以减少印制电路板的面积,还可以减少电磁干扰,从而有利于系统更加稳定的工作。在不影响系统工作速度的条件下,在系统设计中利用串行接口代替并行接口不失为一种很好的设计方法。

参考文献

1 TMS320C54X DSP Reference Set Volume5: EnhancedPeripherals. TI公司, 1999

2 AD73360 Data Sheet.AD公司, 1999

3 苏 涛. DSP实用技术.西安:西安电子科技大学出版社,2002

评论