基于SoC的实时信号处理系统中存储系统

容错存储系统的硬件支持

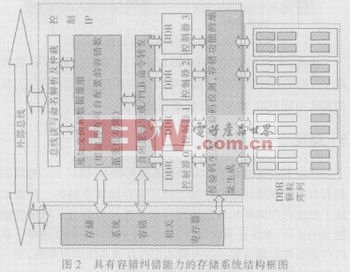

具有容错纠错能力的存储系统的结构图如图2所示。存储系统的容错方案和不考虑容错的存储系统相比,需要在原有模块的基础上进行修改并增加一些设计。主要包含以下几个方面:

(1)增加存储颗粒。为了实现存储系统的容错和纠错能力,增加一定数量的存储颗粒是必须的。在存储颗粒阵列中增加冗余的行列按照行列的二级冗余存储形式组织。为了适应SoC实时信号处理系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。

(2)在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。

(3)增加纠错码编码解码模块具有容错功能的地址生成。纠错码可以采用多种方式,如海明码、CRC码等。具有容错功能的地址生成模块使系统可以根据容错寄存器的内容,重新生成数据的写入地址和读出地址。

(4)增加自测逻辑生成模块。当软件命令配置了寄存器开始进行自检时,自测逻辑不再处理总线上接收的命令,自动生成测试用代码和地址进行写读检测,使系统可以根据对存储颗粒的工作状态进行有效的分析,并且当发现硬件故障时,就修改寄存器空间中的相关寄存器,以便系统自动启动纠错和容错功能。

(5)修改地址变换和数据重组功能模块。修改后的数据重组需要依据寄存器空间中的故障情况对数据进行重新组织,以便达到容错和纠错的功能。

冗余存储颗粒的组织

为了实现存储系统的容错,在存储颗粒阵列中采用行列二级冗余组织模式。但是根据SoC系统的特点,需要对存储系统颗粒阵列的信号连线进行有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持包含纠错容错转换的总体方案。设计具有纠错容错功能的存储系统主要需要考虑以下几个方面:①系统的纠错能力。②系统的容错能力。由于存储系统受到辐射的影响,可能会发生不可逆转的硬件错误,这时候可以启动系统中的冗余模块来实现容错功能。容错系统正常工作的概率是系统容错能力的衡量标准。③冗余存储颗粒的数目。加入冗余颗粒是实现容错存储系统的必要条件,但是冗余颗粒的位置、连接方式和控制策略等方面都会影响整体的容错能力,用尽量少的冗余存储颗粒实现尽量强的容错功能是系统的设计目标。④需要增加的管脚数目。存储颗粒的数目以及存储颗粒的组织方式都会影响实时信号处理系统需要外连的管脚数目。

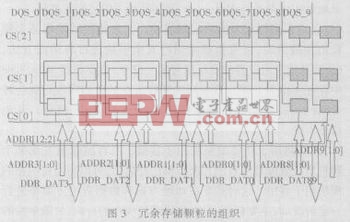

在综合考虑了以上四个方面以后,形成了具有容错纠错的存储系统中颗粒的排放方式。在原系统中,共有16片512Mbit的存储颗粒,组织方式如图3所示。

在容错颗粒组织方式中,冗余存储模块的基本排放采用的是行列二级冗余模式。为了适应实时信号处理器的特点,新方案对存储系统颗粒阵列的信号连线进行了有针对性的修改,从而使系统能通过软件配置或硬件自检来实现纠错或容错,并有效地支持了包含纠错容错转换的总体方案。设在系统中增加i排j列存储颗粒,则用Mem(i,j)表示此时的容错存储系统。信号线所需要的改动包括如下几个部分:

(1)每列的颗粒。需要新的8bit数据线,新的地址线低2bit,每列增加一根DQS信号线。

(2)每排增加的颗粒。数据和地址与已有的每排颗粒复用,每排增加一根CS片选信号。

(3)除CS之外,所有颗粒共用所有控制信号。存储系统增加冗余存储颗粒后,存储颗粒、信号连线和所占管脚都需要相应地增加。Mem(i,j)存储系统中关于颗粒需要增加的资源包括:①共需要8i+2j+ij个冗余颗粒。②共需增加i根CS信号,j根DQS信号,2j根低位地址信号,8j根数据信号。这样对于实时信号处理器,共需增加管脚数为i+11j,Mem(i,j)存储系统所具有的容错能力以及Mem(i,j)的选择将在第4节进行详细讨论。

逻辑设计对容错的支持

为了实现纠错容错方案,必须在逻辑设计上作出相应的改动,主要包括:①为容错系统分配一定的寄存器地址空间。②增加纠错码生成、纠错码解码模块,具有容错功能的地址生成。③增加自测逻辑生成模块。④修改地址变换和数据重组功能模块。

容错系统的相关寄存器

为了实现整个存储系统的容错和纠错,需要在寄存器堆中为容错系统分配一定的寄存器地址空间。这些寄存器地址空间由多个部分组成,主要包括:系统工作状态寄存器,记录系统各个存储期间的状态;系统纠错方案配置寄存器,配置系统可以采用的纠错方式和纠错能力。相关寄存器的功能定义如表1所示(以Mem(i,j)为例)。

评论