基于USB和FPGA的随机数发生器验证平台

摘要:为了方便基于FPGA实现的随机数发生器的验证与演示,以CycloneII FPGA芯片EP2C20Q240C8N为核心,设计实现了随机数发生器IP核下载与测试的开发验证平台,并详细阐述了各模块的设计原理及关键技术。最后,通过下载运行随机数生成系统,对整个平台功能进行了检验。结果表明,各模块电路工作正常,平台性能稳定。

关键词:FPGA;随机数发生器;验证平台

引言

随机数发生器是信息安全领域不可或缺的重要组成部分,广泛应用于金融、军事等信息安全保密通信的电子设备中。目前,随着对RNG体积、功耗、接口方式等要求的提高,设计集成化芯片或IP核形式的随机数发生器成为一种必然。为此,基于纯数字电路实现的随机数发生器已成为研究的热点,而FPGA可编程逻辑芯片为此类随机数发生器的研究提供了良好的开发环境。

为方便随机数发生器IP核的下载、运行及测试,同时保证产生的随机数能够快速地传送给主机进行随机性检测,本文以FPGA芯片为核心,以USB接口为通信接口,设计实现了一个随机数发生器的验证平台。该平台结构简单,功能完善,对于其他特殊应用的验证平台搭建也具有指导意义。

1 系统硬件结构及工作原理

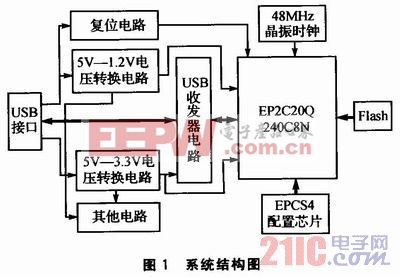

随机数发生器验证平台主要由CycloneII FPGA芯片EP2C20Q240C8N、与主机进行通信的USB收发器电路、下载配置芯片EPCS4、频率为48 MHz的时钟源芯片、外部存储器(Flash)、两个电压转换电路、复位电路和其他电路组成,如图1所示。

在每次实验演示时,将该芯片通过USB口与PC机相连,由主机为平台提供5 V电源,当与主机连通后系统上电,复位电路进行工作,对整个系统进行复位。以QuartusII 7.2为开发环境,采用ByterBlsterII下载电缆,通过JTAG下载口或以AS下载方式,通过配置芯片EPCS4将随机数发生器系统下载到实验平台中,最终通过USB口连接主机与平台进行信息交互。由主机向系统发送命令,在系统控制下,产生的随机数通过USB收发器传送给主机,主机接收数据后进行随机性的各项检测。

2 核心器件和关键技术

2.1 FPGA芯片EP2C20Q240C8N

EP2C20Q240C8N芯片是A1tera CyeloneII系列产品中的一员,它采用TSMC1.2 V、90 nm和低电介绝缘工艺技术,由12英寸(300 mm)晶圆制成,具有潜在速度方面的极大优势。

评论