Innolink-国产首个物理层兼容UCIe标准的Chiplet解决方案

芯动准备了满满一桌的大餐 等着UCIe这个客人上桌!

本文引用地址:http://www.eepw.com.cn/article/202204/432948.htmInnolink™ Chiplet是芯动先进IP之集大成者,代表着国内乃至世界领先水平,闻之不如见之,我们来盘点一下其内部实现的基础技术。

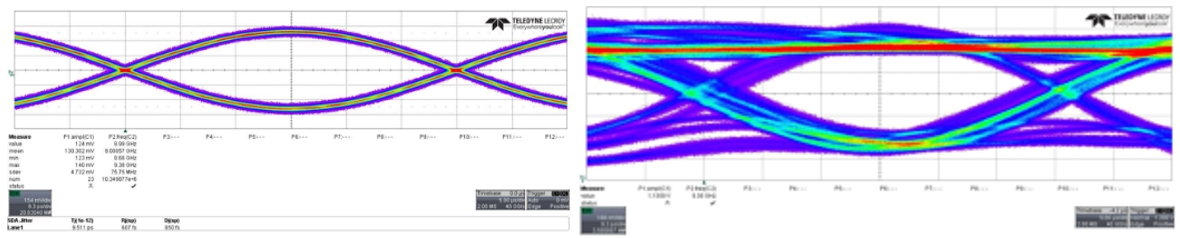

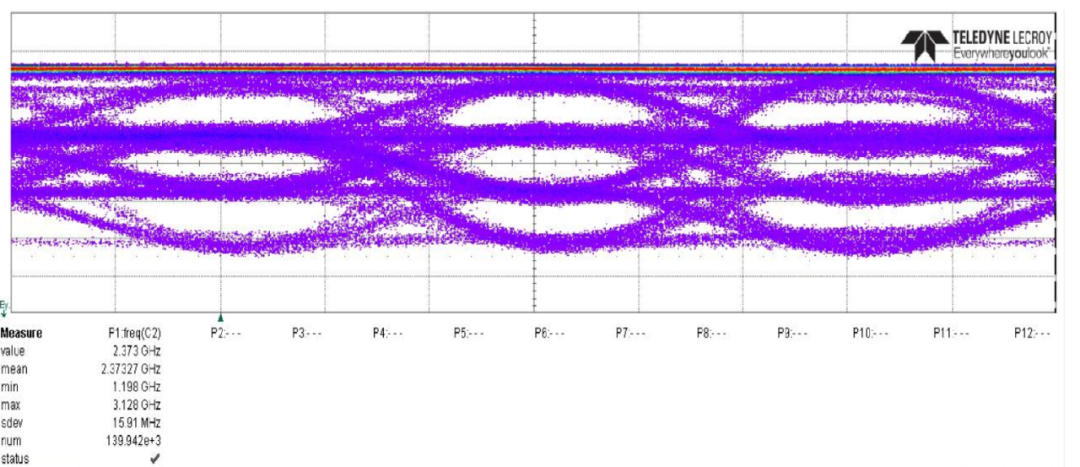

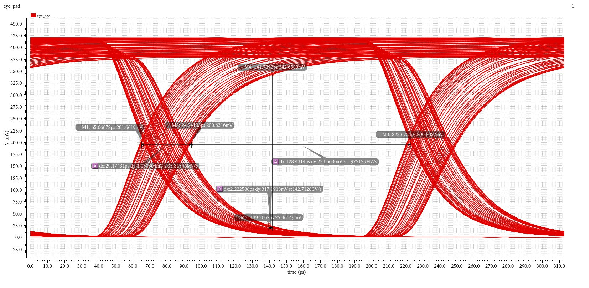

▲ 18Gbps GDDR6 单端信号量产验证

▲ 21Gbps PAM4 DQ eye, single ended

▲ HBM3 6.4Gbps 高速眼图

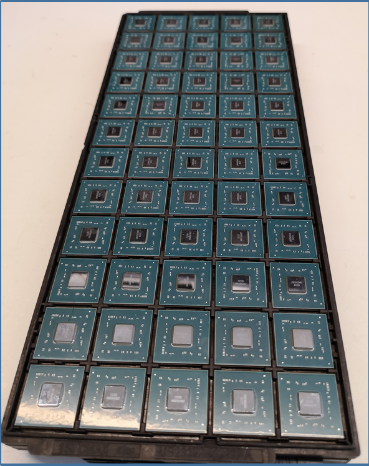

▲ 全球首个GDDR6/6X combo IP量产

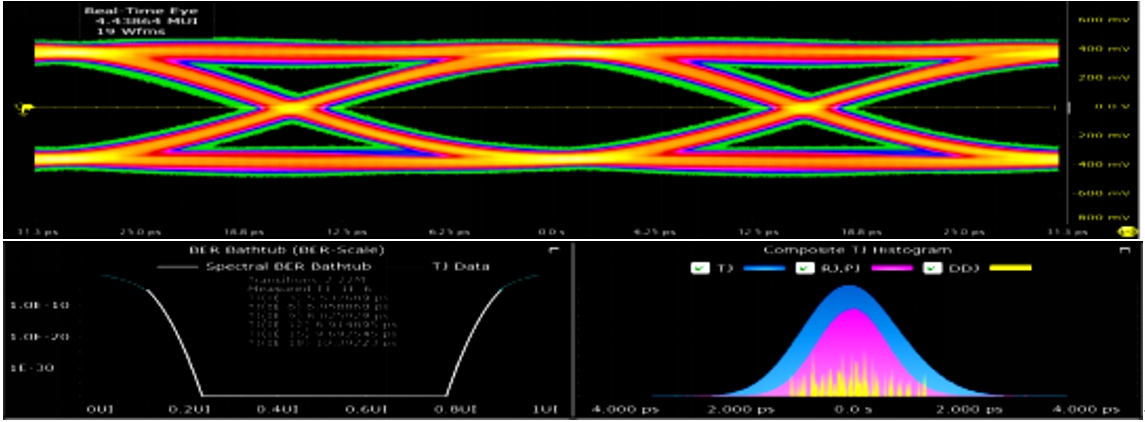

▲ 32/56G SerDes眼图

▲ 风华1号4K高性能GPU应用Innolink™ Chiplet实现性能翻倍

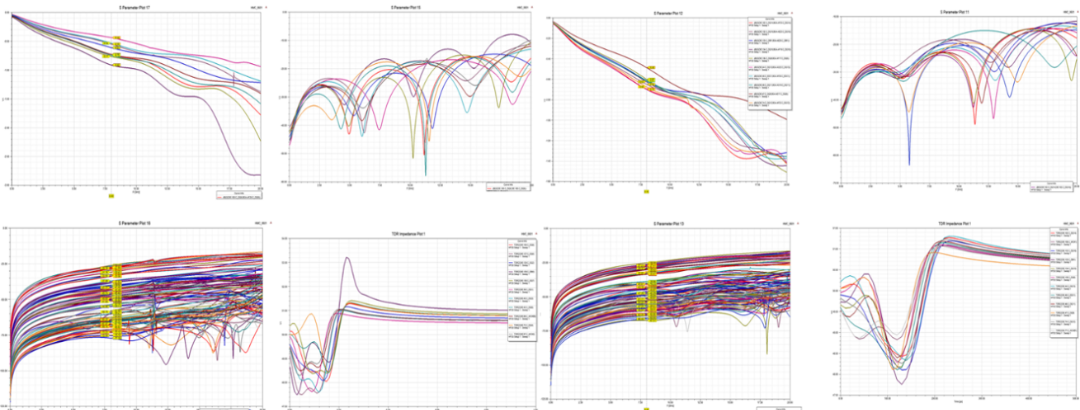

▲ 先进封装信号完整性分析

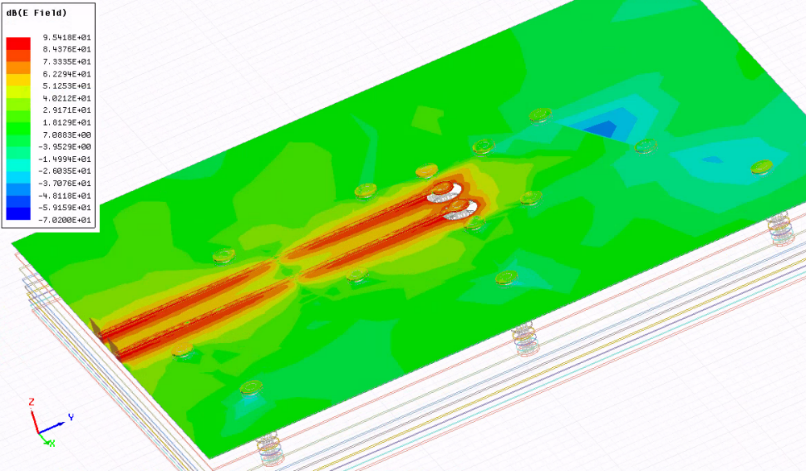

▲ 封装热效应仿真

看到这些赏心悦目的IP验证测试眼图,相信大家对Innolink™ Chiplet有了更加客观的认知。追本溯源,这些成果反映的另一问题也值得探讨,为什么芯动能在这么多先进技术上取得如此耀眼的成绩?

为什么要做先进IP?有哪些挑战和困难?

芯动科技的CEO敖海先生是技术出身,长期保持和一线研发工程一起讨论架构、改代码、调电路、定方案的习惯,从领导人至一线员工,全公司都秉承踏实进取、勇于创新、务实精进的作风。见微知著,芯动研发团队能持续攻克一个个技术难关、攀登一座座行业高峰也就不奇怪了。正因于此,芯动才能保持对市场的敏锐判断和技术发展的持续领先!

▲ CEO亲自参与研发工作,带领团队勇争领先!

敖海认为,现阶段先进工艺芯片技术迅速发展、高性能应用需求急剧增加,只有不畏挑战迎难而上、抢先占领技术高地,在Chiplet等先进IP技术上对标海外巨头,并在某些领域实现弯道超越,才能在市场上站稳脚跟,有效赋能国产半导体发展!

▲ 芯动科技CEO敖海先生

首发先进IP技术具备很多优势,可以快速赢得业界认可、第一时间导入客户需求并设计验证、广泛获得Foundry和封测等上下游的大力支持。在市场应用成熟时,还可以让广大芯片客户用上量产验证的、可靠安全的IP,从而根据新的升级方向迅速实现技术迭代,进一步推动业务增长。一步领先、步步领先,从IP切入是极具实际意义的。

当然,首发推出先进工艺IP面临很多困难:

1.没有参照对象,试错成本高。

第一个吃螃蟹的人,先进道路的开拓者,总要付出加倍的努力。在很多大的技术节点上并没摸石头过河的说法,需要不断的摸索尝试。通俗点讲就是一个个坑踩个遍,踩结实了,路就平了。

2.对团队要求高。

一个先进IP,从数字到模拟、后端到工艺、流片到封测,每个环节都要资深的技术人员,芯动经过16年的积累,打造一支技术过硬的队伍,后来居上,面对国外厂商的先发优势毫不退让,用实力赢得全球客户认可。

3.先进工艺流片验证成本高。

先进工艺的IP流片验证成本很高昂,设计工时、FinFet工艺MPW或者流片费用、封测等累加,每次验证的费用轻轻松松破百万美元。

某种意义上,芯动在先进IP领域获得的优势和业界认可,以及6大合作晶圆厂在工艺、流片成本、产能上给予的巨大帮助,都是做先进工艺IP的好处。

先进IP的重要意义

有和没有先进IP区别是很大的,有先进IP能够使市场更加理性,同时满足国产高端芯片自主可控、技术迭代的迫切需求!

▲ 芯动科技主办的2021国产IP与定制芯片生态大会盛况

芯动的先进IP技术,一方面引领行业技术的创新,塑造半导体企业的全球化长远发展视野,另一方面填补国内高性能芯片的应用空白,助力国内高端芯片发展。

芯动16年来重兵投入全球先进工艺、专注国产自主IP研发,在高性能计算平台、多媒体终端&汽车电子平台、IoT物联网平台等应用领域打造了核心优势,超过200次的流片记录、逾60亿颗授权量产芯片、10亿颗以上高端定制SoC量产,默默耕耘、脚踏实地,为赋能高端芯片做出重要贡献!

评论