苹果发布“合二为一”芯片,华为公布“芯片叠加”的专利

昨日凌晨的苹果春季发布会上,苹果发布了最强的 “M1 Ultra”芯片。

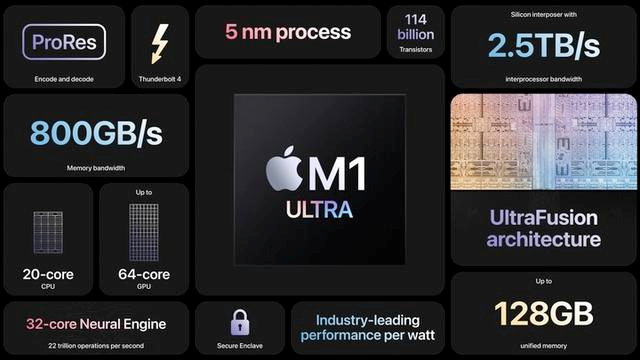

本文引用地址:http://www.eepw.com.cn/article/202203/432003.htm在大会上,苹果公布了 M1 Ultra 芯片很多牛逼的参数,比如:晶体管数量1140亿颗;20核CPU(16 个高性能内核和 4 个高效内核);最高64核GPU;32核神经网络引擎;2.5TB/s数据传输速率;800GB/s内存带宽;最高128GB统一内存。

M1 Ultra 是 Apple 芯片的又一个游戏规则改变者,它将再次震撼 PC 行业。通过将两个M1 Max 芯片与我们的 UltraFusion 封装架构相连接,我们能够将 Apple 芯片扩展到前所未有的新高度。

苹果公司硬件技术高级副总裁Johny Srouji表示:“凭借其强大的CPU、庞大的 GPU、令人难以置信的神经引擎、ProRes 硬件加速和海量统一内存,M1 Ultra 完善了M1系列,成为世界上最强大、功能最强大的个人计算机芯片。”

众所周知,要做更强大的芯片,就需要堆更多的电路,更多的晶体管,而工艺越先进,同样的面积就能塞进去更多晶体管,芯片性能上限就越高,这也是为何大家追求更先进制程的原因之一。

但在当下的工艺技术条件下,晶体管多了,良率就会降低,良率低了,那每个芯片就会变得非常昂贵,那么如何才能在降低成本的前提下,做出超越极限的芯片呢?

苹果的做法是采用M1 Max中隐藏的芯片互连模块,通过UltraFushion架构把两块芯片像拼拼图一样“合二为一”。

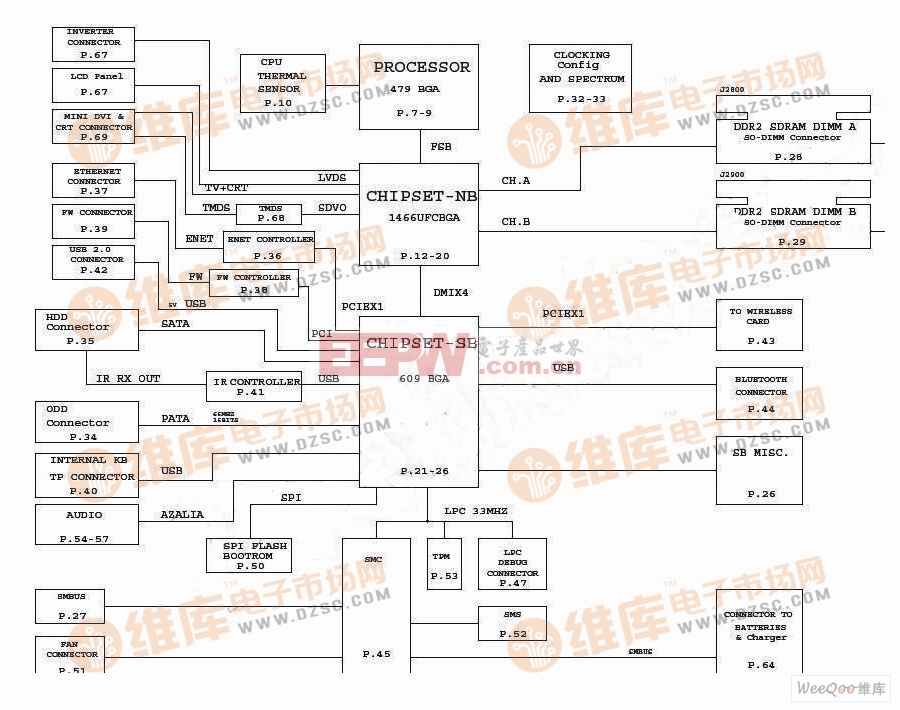

苹果的“UltraFushion”其实就是Die to Die Connection,就是在芯片设计时在同一个封装(package)里面使用多枚硅片(silicon),并且在其中设计极其高速的互联通道,使得这两块硅片可以形同一块芯片一样共同工作。

UltraFusion使用了1万条DTD连接,提供了高达2.5TB/s的互联速度,它的带宽极高、能耗极低,而且由于是数块die共同封装,其对良率的敏感度要远低于一块超巨型芯片,因此DTD也被认为是未来芯片性能发展的一条具有巨大潜力的道路。

值得一提的是,M1 Max是一个基于小芯片(Chiplet)的设计中将多个芯片堆叠在一起的芯片模块(MCM),其2-tile的规格使其从CPU到GPU到NPU到内存带宽到内存容量,全部都是2xM1 Max的规格。

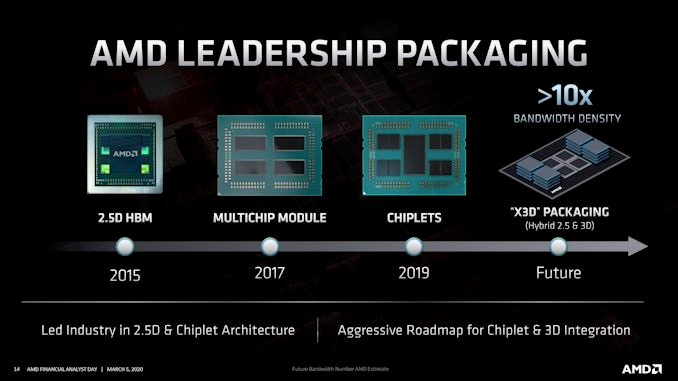

当然这条道路也不是只有苹果在走,AMD 早在 2017 年就引入了MCM 并且在 2019 年引入了Chiplet 设计,未来的发展趋势是进一步提升堆叠能力,实现所谓的 3D 堆叠,也就是不仅在 2D 上扩展,还要在垂直方向上扩展。

而国内企业有同样思路的就是华为海思了。在2021年5月份的时候,华为将“双芯叠加”的专利进行了公开,并表示14nm技术可以到达7nm的性能,此消息一出顿时在世界范围内引起热议,得到全球的关注。简单来讲14nm与7nm之间,它们的主要差别就是在芯片面积相同的情况下,7nm可以拥有更多的晶体管数量,在性能方面自然也会有所提升。

知乎用户@超合金彩虹糖表示,这颗M1Ultra是苹果野心的进一步延续,连最有钱的苹果也转向Chiplet了,这预示着也许未来在消费级领域,高性能产品走Chiplet这条路可以走得通。目前来看,芯片组合叠加已经从理论变成现实,从芯片封装的角度来看,逐渐从2.5D封装走向3D封装,芯粒(Chiplet) 将提供最佳性能和最大灵活性。台积电、英特尔、三星、AMD等十家公司已经行动了,联合创建UCIe联盟。(详情:英特尔、AMD、Arm等九大企业宣布UCle开放标准,推动Chiplet发展)

UCIe联盟创建的初衷是将小芯片打造成开放,互联的产业发展生态,让不同客户也能通过各类小芯片产品满足更多的需求。

未来,以Chiplet模式集成的芯片会是一个“超级”异构系统,可以带来更多的灵活性和新的机会。

芯原股份创始人、董事长兼总裁戴伟民曾表示,对于产业来说,Chiplet带来了新的机会,在标准与生态层次上,Chiplet建立了新的可互操作的组件、互连协议和软件生态系统;对于芯片制造与封装来说,增设了多芯片模块 (Multi-Chip Module,MCM) 业务,Chiplet迭代周期远低于ASIC,可提升晶圆厂和封装厂的产线利用率;对于半导体IP来说,升级为Chiplet供应商,可提升IP的价值且有效降低芯片客户的设计成本;最后对于芯片设计来说,降低了大规模芯片设计的门槛。

戴伟民建议国内企业持续推进Chiplet量产和2.5D/3D封测技术开发。

评论