采用SiC FET尽可能提升图腾柱PFC级的能效

图腾柱PFC电路能显著改善交流输入转换器的效率,但是主流半导体开关技术的局限性使其不能发挥全部潜力。不过,SiC FET能突破这些局限性。本文介绍了如何在数千瓦电压下实现99.3%以上的效率。

本文引用地址:http://www.eepw.com.cn/article/202105/426022.htm正文

交流输入电源的设计师必须竭力满足许多要求,包括功能要求、安全要求和EMC要求等等。他们通常需要进行权衡取舍,一个好例子是既要求达到服务器电源的“钛”标准等能效目标,又要用功率因素校正(PFC)将线路谐波发射保持在低水平,以帮助电网可靠高效地运行。在大部分情况下,会通过升压转换器部分实施PFC,升压转换器会将整流后的主电压升为高直流电压,而脉冲宽度调制迫使线路电流符合正弦波和线路电压的相位。虽然PFC级无法避免损耗,但人们在设计时耗费了大量努力来提高效率,使得从交流输入电转为高压直流电时可接受的最低效率也要超过99%。

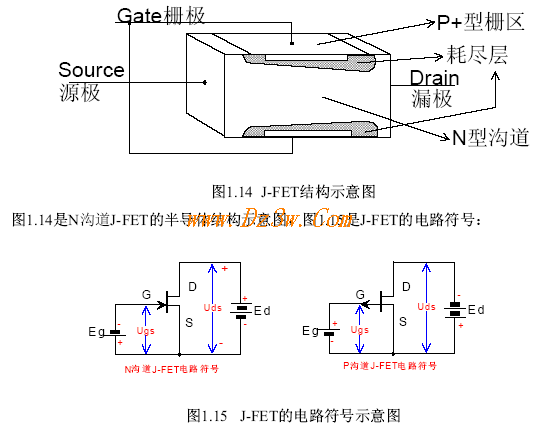

图腾柱PFC级的导电路径中的组件较少

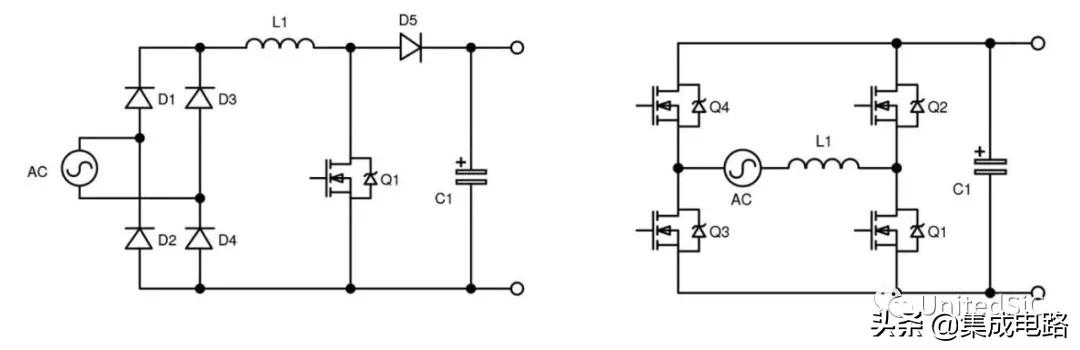

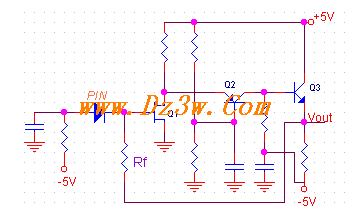

桥式整流器可为单独的升压级提供整流后的交流电,如图1(左)所示。该方式被广泛采用,以获得有效的功率因数校正,但是仅二极管中的损耗就可以轻松超过整体损耗预算的1%。图腾柱PFC级(TPPFC)是更好的解决方案,如图1(右)所示。

【图1:桥式整流器输入(左)和图腾柱PFC级(右)】

在TPPFC电路中,当连接到L1的交流电主线路为正压时,Q1是升压开关,Q2是同步整流器,Q3导电以允许线路电流循环而Q4阻断电路。当交流输入电压为负压时,Q1和Q2角色互换,Q3阻断电路而Q4导电。无论何时,在TPPFC级中,导电的器件要比桥输入PFC少一个,而整体压降仍较低,因为所有二极管都被同步整流器取代了。Q1和Q2像在普通升压转换器中一样在高频下开关,而Q3和Q4以线路频率交替导电,因此只有它们的导电损耗会产生重要影响。

必须选择PFC级导电模式

设计师们可以选择运行模式与任何升压转换器,这与L1中存储的能量是否在每个周期内完全转移到输出中有关。这相当于每个周期的电感电流都跌到零(断续导电模式,DCM)或持续为正(连续导电模式,CCM)。还可以安排电路在二者的临界线上运行(临界导电模式,CrM),这需要开关频率可随着负载和线路变化而变化。这些模式有各自的优缺点,DCM电路有软打开开关,可实现低损耗,但是在关闭时dV/dt相关的EMI很高,而且峰值电流电平过高,从而使得该模式不适合大功率应用。CrM有变频运行的缺点,而且虽然CrM中的峰值电流较小,但是除非各级交错否则它们产生的导电损耗仍不可接受,而各级交错会产生相关成本和复杂性。CCM峰值电流最低,导电损耗也最低,但是电路采用“硬开关”方式来打开和关闭,同时经过的电流大,这导致如果使用基于硅的功率开关可能会造成大损耗。在这些损耗中占据主要部分的是高频升压同步整流器体二极管的反向恢复电荷QRR和升压开关的输出电容COSS,该电容在每个周期中都会充电和放电。这些影响十分严重,以致直到不久前,在采用市面上的半导体器件的情况下,这些拓扑并不具备可行性。

宽带隙半导体就是解决方案

碳化硅(SiC)和氮化镓(GaN)被视为未来的功率半导体,有许多人撰文称赞它们的低导通损耗和低开关损耗这两种值得大力宣传的优点。自然而然地,可以考虑将它们用于TPPFC电路,而且它们确实让电路变得可行。SiC MOSFET的性能比硅MOSFET好,体二极管反向恢复电荷QRR低80%或更多,输出电容COSS也较低。然而,同步整流器导电前,在“死区时间”,体二极管的正向压降非常高。采用SiC MOSFET时的栅极驱动偶尔也会有阈值迟滞现象和可变性方面的问题,而且全面增强的栅极电压与最大绝对值之间的裕度小。

GaN器件没有体二极管和反向恢复问题,但是为了实现最佳效率和低阈值电压,栅极驱动很复杂,并伴随虚假打开风险。GaN HEMT单元仍然相对昂贵,且适合较低的功率范围,没有雪崩能力。

SiC FET仍是较好选择

SiC FET是保留了SiC MOSFET最佳方面而无其缺点的器件,它是高压SiC JFET和低压Si-MOSFET的共源共栅组合。该器件速度快,导通电阻很低,但是栅极驱动简单,兼容Si-MOSFET甚至IGBT电平。它的阈值电压很高,无迟滞现象,距离最大绝对额定值有很好的裕度。该器件具有由低压Si-MOSFET定义的体二极管效应,QRR极低,正向压降仅为1.75V左右,同时输出电容COSS也低。它具有可防止过压的雪崩效应。

SiC FET由UnitedSiC率先制造,现已推出第四代产品。第四代产品改进了单元密度以降低单位面积的导通电阻(RDS.A),运用银烧结粘接和晶圆减薄技术改进了热设计,从而尽量减小了到基片的热阻。

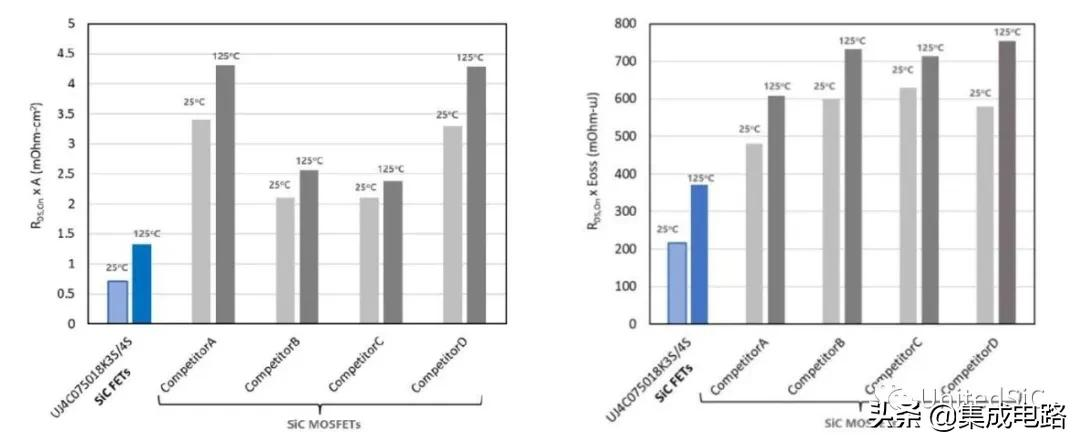

只有在考虑了权衡取舍的特征后,对比SiC FET和相同器件电压级的其他技术才有意义。因此,查看给定性能下每个晶圆的晶粒的RDS.A和RDS.EOSS(衡量如何权衡硬开关损耗和导电损耗的指标)等性能表征会很用。图2显示的是第四代750V UnitedSiC SiC FET器件与类似的650V SiC MOSFET器件在25°C和125°C下的对比。SiC FET的优势很明显,而额定值还高100V,这很实用。

【图2:SiC FET与SiC MOSFET对比】

实际结果证实了SiC FET的优势

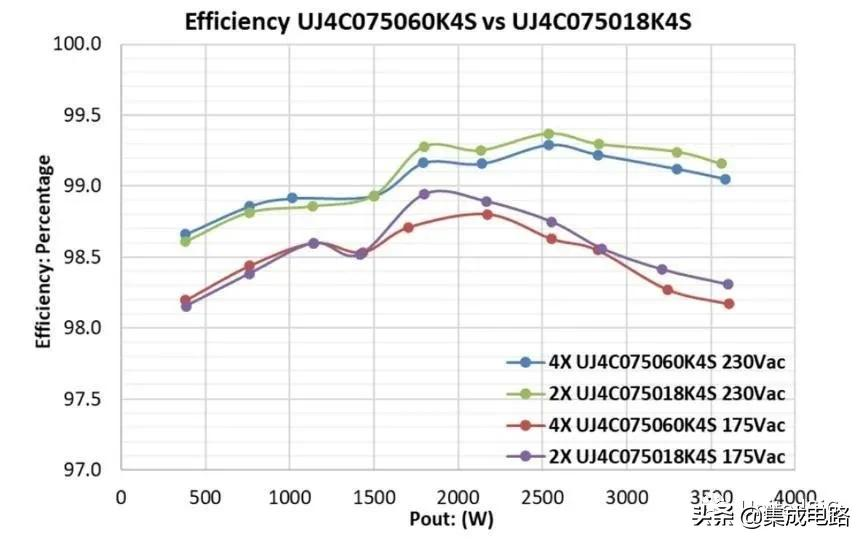

UnitedSiC使用额定值为750V,18毫欧,采用TO-247-4L开尔文连接封装的第四代UJ4C075018K4S器件构建了图腾柱PFC级演示板。PFC级的额定值为3.6kW 85-264V交流输入电压和390V直流输出电压。两个SiC FET用于60kHz高频开关支路,四个28毫欧硅超结MOSFET用于“慢”支路。图3显示的是效率曲线,在230V交流电压和2.5kW输出下,效率达到99.37%的高峰。为提供更多信息,图中还显示了成本较低的60毫欧SiC FET器件的曲线(在每个位置并联两个该器件)。

【图3:使用SiC FET的3.6kW图腾柱PFC级的效率】

在对成本非常敏感的应用中,图1中的Q3和Q4可以替换成标准硅二极管,这样,在描述的演示板中,效率仍能超过99%。如果采用桥式整流器,则最好多使用两个二极管来实现突波保护,防止升压电感在启动时瞬间饱和。

使用FET-Jet计算器可轻松选择SiC FET

为了方便选出适合的 SiC FET,UnitedSiC提供了一种基于Web的设计工具,FET-Jet计算器。这款交互工具包含用于各种拓扑的隔离和非隔离直流转换器以及交直流转换器的预先编程的应用电路,包括简单的升压PFC和图腾柱PFC等。它也支持CCM和CrM模式。使用者可以从下拉列表中为每个应用选择SiC FET,然后该工具会瞬间计算出整体效率、损耗(并按开关损耗和导电损耗进行分析)、结温和当前应力水平。可以选择要并联的器件,以实现较高功率。如出现无效输入,计算器会发出警告。该工具免费使用,且无需注册。

图腾柱PFC级是一种有吸引力的方法,有望实现更高的效率和更简单的设计,但是直到不久前,半导体技术也未能让它发挥出全部潜力。在SiC FET的帮助下,该电路现在走入了工程师们的视野,用于在交流输入转换器中将功耗降低至更低水平。

评论