台积电最新进展:2nm正在开发 3nm和4nm将在明年面世

全球最大的晶圆代工厂,拥有近500个客户,这就是他们的独特之处。一方面,公司几乎可以为提出任何需求的所有客户提供服务;另一方面,就容量和技术而言,他们必须领先于其他任何人;就产能而言,台积电(TSMC)是不接受任何挑战,而且未来几年也不会

本文引用地址:http://www.eepw.com.cn/article/202105/425190.htm台积电今年300亿美元的资本预算中,约有80%将用于扩展先进技术的产能,例如3nm,4nm / 5nm和6nm / 7nm。分析师认为,到今年年底,先进节点上的大部分资金将用于将台积电的N5产能扩大,扩大后的产能将提到至每月110,000〜120,000个晶圆启动(WSPM)分析师估计,台积电的N5晶体管密度约为每平方毫米1.7亿个晶体管(MTr / mm 2),如果准确的话,它是当今可用的最密集的技术。相比之下,三星Foundry的5LPE的晶体管密度介乎125 MTR /平方毫米〜130 MTR /平方毫米之间,而Intel的10纳米设有一个约100 MTR /平方毫米的密度。

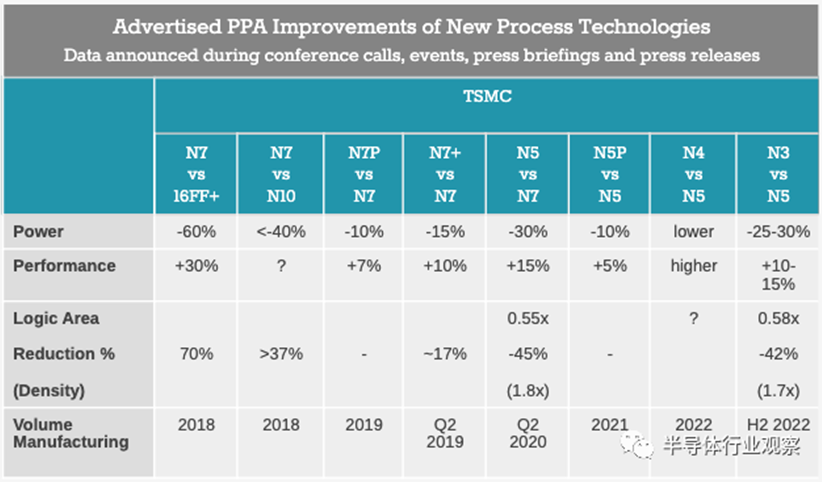

魏哲家说:“ N4将利用N5的强大基础来进一步扩展我们的5 nm系列。” “ N4是具有兼容设计规则的N5的直接移植,同时为下一波5纳米产品提供了进一步的性能,功率和密度增强。N4风险生产的目标是今年下半年,到2022年实现批量生产。

2022年,全球最大的芯片合同制造商将推出其全新的N3制造工艺,该工艺将继续使用FinFET晶体管,但预计PPA将大幅提升。

N3将进一步增加EUV层的数量,但将继续使用DUV光刻技术。而且,由于该技术一直在使用FinFET,因此不需要从头开始重新设计和开发全新IP的新一代电子设计自动化(EDA)工具,这可能会成为基于Samsung Foundry基于GAAFET / MBCFET的3GAE的竞争优势。。

台积电首席执行官说:“ [N3]风险生产计划在2021年进行。” “目标是在2022年下半年实现量产。引入N3技术将成为PPA和晶体管技术中最先进的铸造技术。[…]我们对我们的[N5]和[N3]充满信心,他们将是台积电的大型持久节点。”

Gate-all-around FETs(GAAFET)仍是台积电发展路线图的一部分。预计该公司在其“后N3”技术(可能是N2)中使用新型晶体管。实际上,该公司处于下一代材料和晶体管结构的探路模式,这些材料和晶体管结构将在未来的许多年中使用。

该公司在最近的年度报告中说:“对于先进的CMOS逻辑,台积电的3nm和2nm CMOS节点正在顺利进行中。” “此外,台积电加强了探索性的研发工作,重点放在2nm以外的节点以及3D晶体管,新存储器和low-R interconnect等领域,这些领域有望为许多技术平台奠定坚实的基础。

至少按台积电董事长刘德音、德国智库Stiftung Neue 4月初,台积电董事长刘德音公开提到,美国和欧洲扩大其半导体晶圆厂产能的计划是“经济上不现实的”,因为这些计划是为了满足其自身需求而进行的,如果整个半导体供应链转移到美国和欧洲,或者如果这些地区计划扩大产能,则将导致大量“非盈利性”企业的产生。

评论