应用于微显示芯片的MIPI DSI驱动接口设计

尹 远,黄嵩人 (湘潭大学 物理与光电工程学院,湖南 湘潭 411105)

摘 要:随着信息技术发展,高分辨率的微显示器已广泛应用于移动电子设备中,传统显示接口难以满足其高 速率传输、低功耗、抗干扰、兼容性高等要求,因此本文针对以上问题,提出了一种基于MIPI DSI协议,并应 用于高分辨率微显示芯片的显示驱动接口的设计。

0 引言

微显示芯片是一种特殊形态的显示器,其物理尺寸 小,功耗较低,分辨率高,目前主要应用的产品形态 有:LCOS微显示器,OLED微显示器,LCD微显示器 等。也可以通过光学系统产生大屏幕系统,常用于投影 系统和近眼显示系统中[1]。其应用领域广泛,如VR眼 镜、AR智慧眼镜、军用头盔、微型投影仪、车载抬头 显示等电子设备。

随着消费级电子设备的发展,微显示芯片应用的电 子产品越来越多,显示的分辨率不断增强,对显示效果 的要求也日益提高,需要传输的数据量和速率也越来越 大,同时还要求设备保持高性能和低功耗,传统的显示 接口已满足不了诸多要求。因此本文针对这种情况,设 计了一种适用于高分辨率微显示芯片的MIPI DSI显示驱 动接口[2]。

1 MIPI DSI协议介绍

MIPI DSI是MIPI(Mobile Industry Processor Interface,移动业处理器接口)联盟为了对移动设备的外设接口标准进行统一,以提高系统兼容性、设计性能 和效率,而提出的一种显示接口标准[3]。DSI接口是一 种高速的串行显示接口,可实现高分辨率显示,而且有 功耗低、抗干扰强的特点[4]。

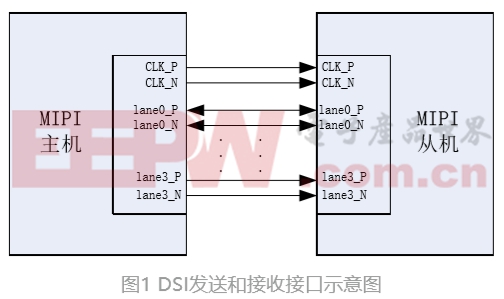

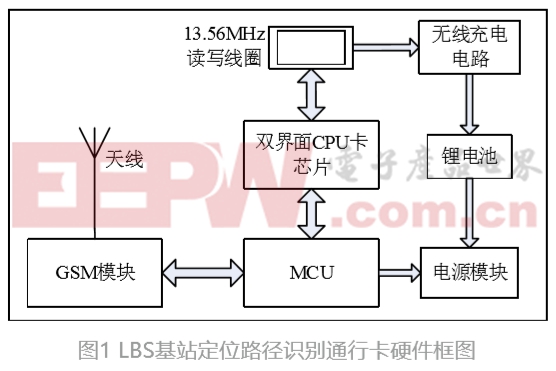

图1所示是简化的DSI接口示意图[5],主机可以发送 高速像素数据和低速命令给从机,并可以从从机设备中 读取状态或像素信息。主机和从机之间的通信一般是配 置1对差分时钟通道,1~4对数据通道。

MIPI DSI支持两种基本操作模式,分别为命令模式 (Command Mode)和视频模式(Video Mode)[3]。命令模式是指主机端向从机设备发送命令和数据,转换为 DBI格式,对显示设备进行读写操作,以此来间接控制 从机端的外围设备的工作状态。另外从机端会通过双向 的数据通道0返回相关数据,主机端因此也可以读取到 从机设备的状态信息和缓存内容。视频模式主要是通过 数据通道在高速传输模式下,由主机单向传输给从机以 图像显示或视频数据,从机接收到进行解码后,最终将 其转为DPI时序格式直接传送给显示设备,进行实时显 示[4]。

DSI接口支持两种传输模式,分别为高速数据传输 模式(High-Speed Mode)和低功耗模式(Low-Power Mode)[6]。其中所有的数据通道都可以用于单向的高速 数据传输,如传输图片和视频数据。低功耗模式下的传 输只通过双向的lane0进行,如低速数据和控制命令,速 率可达10 Mbit/s。时钟通道传输高速传输过程中的同步 时钟信号,采用高速DDR时钟,速率可达到1 Gbit/s。

MIPI DSI协议中规定数据是以数据包的形式传输, 根据包的长度不同,分为长包和短包。短包固定4个字 节长度,由标识符DI、data0、data1、ECC校验码组成 [6],如图2所示。长包是由包头、包数据、包尾组成,如 图3所示。包头是由DI、指定数据包中数据个数的WC、 ECC码组成,包尾是16 bit的校验和,长包的总长度范 围为6~65541字节[6]。

2 DSI接口工作原理

本文的设计目标是实现基于MIPI协议的显示接口 的设计,支持4路通道的高速数据传输,包括图片或视 频,通道0实现Escape模式下的低功耗传输模式,用以传输低速控制命令或数据,且支持lane0双向数据传输, 时钟通道传输高速同步时钟信号,支持RGB888格式的 数据输出,具有ECC校验、CRC校验功能等[3]。

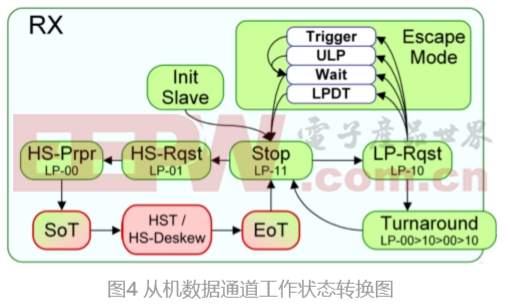

高速模式下,通道上有两种状态:HS-0、 HS-1[7]。在低功耗模式下,lane0上有四种状态:LP00、LP-01、LP-10、LP-11[8]。根据总线上检测到不 同的电平序列后,分别进入或退出相应的模式,如图4 所示为从机通道工作的状态转移图[7],可在高速模式、 Escape模式、TA(Turnaround)模式之间切换。

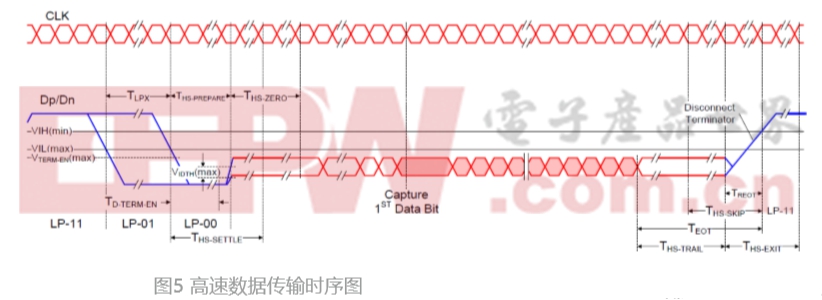

所有的数据通道都支持高速数据传输模式,从机接 收来自主机的高速串行数据进行编解码。在空闲的时间 段,通道处于LP-11状态。当从机端接收到发自主机端 的序列:LP-11→LP-01→LP-00,即高速请求序列, 之后便准备进入高速数据传输模式接收高速数据。如需 退出高速模式,则发送EOT→LP-11。图5为高速传输 时序图[7],定义了整个高速传输过程的方式和时序。当 从机端接收到高速模式下传输的数据后,会将数据包 中的像素数据解析出来,生成RGB格式数据、同步信 息、有效信息等,通过DPI接口输出给显示端进行显示 成像。

当从机检测到主机发送序列:LP-11→LP10→LP-00→LP-01→LP-00,进入Escape模式。之后 等待主机发送8 bit的命令,可进入其中的三种模式: ULPS超低功耗模式、LPDT低功耗数据传输模式、 Trigger模式。除了lane0都支持外,其他数据通道只支持 其中的超低功耗模式。其中使用较多的是低速数据传输 模式,lane0通过此模式可传输控制命令或数据。退出 Escape模式主机需发送序列:LP-10→LP-11。

进入TA模式需要发送请求序列:LP-11→LP10→LP-00→LP-10→LP-00,之后主机会释放总线控 制权,由从机获得总线控制权,通过lane0发送低速数据 返回给主机,数据内容一般是响应信息、错误报告、结 束包等,发送完毕后从机会发送TA模式的序列请求, 将总线控制权交还给主机。退出TA模式发送序列LP00→LP-10→LP-11即可。

3 MIPI DSI电路设计

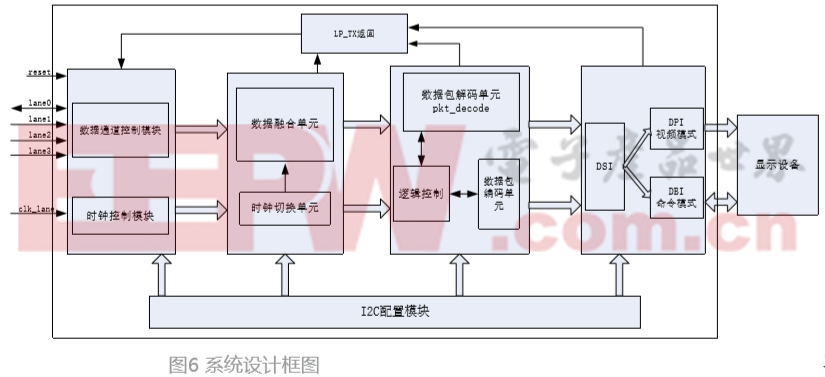

依据MIPI DSI协议的层次划分,将DSI接口电路分 为物理传输层模块、底层协议层模块、通道管理层模 块、应用层模块4个主要模块[3],系统设计方案如图6 所示。

1)物理传输层:本层只要由时钟通道控制模块、 数据通道控制模块组成,其中数据通道控制模块又分 为数据通道0控制模块和其他数据通道控制模块。时 钟通道控制模块,主要实现了检测时钟通道LP→HS和HS→LP的模式切换。数据通道控制模块,主要完成了4 个数据通道的高速模式和低功耗模式相互之间的切换检 测,数据通道0的Escape模式和TA模式的检测[3]。将接 收到的高速模式和低功耗模式下的串行输入数据转为并 行数据,并传输给通道管理层[3]。将TA模式的返回数据 进行并串转化,再通过lane0传输给主机[2]。

2)通道管理层:主要分为高速数据接收模块、低 功耗模式数据接收模 块,以及时钟切换模 块。完成4个数据通道 的高速模式的SOT序 列检测,接收物理传 输层发送过来的低功 耗模式命令和数据[3]。 实现数据融合功能, 将多通道的数据恢复原有字节顺序,并整合起来。时钟 切换模块实现高速时钟、低功耗下时钟,以及TA模式 下的不同时钟的切换。

3)底层协议层:主要完成高速模式和低功耗接收 模式的数据包的解码和编码,及ECC、CRC检测。当接 收来自物理传输层的数据时,对高速和低功耗模式的数 据包进行解码,检测数据包的类型,根据长短包分别 进行处理,并对ECC 码进行检测校验、纠 错,以及CRC校验。 对接收到的低速返回 数据包编码打包,主 动生成对应的ECC校 验码、CRC校验码, 以返回主机以响应 (ACK)和错误报告 (Error Report)[3]。 另外需要处理来自物理层的错误信号和Trigger信号,以 及本层内检测出的ECC校验错误和CRC校验错误[4]。

4)应用层:这部分直接与显示端连接,将接收到 的数据和命令进行译码,分别可以进入视频模式和命 令模式,最后转换成显示端能识别的DBI格式或DPI格式。进入视频模式后,将接收到的高速像素数据转为符 合显示端兼容的DPI时序的数据,然后进行显示。当进 入命令模式,将低功耗接收的数据包解码,之后转成 DBI格式数据写到相应寄存器中。有时还需要从显示端 读到的DBI格式,然后将其编码转为DSI接口数据,最 后通过lane0发送给主机。

另外还有I2C配置模块,用于对各模块进行参数配 置,确保设计的成功实现,也可方便验证和芯片调试, 提高该设计的灵活性和兼容性。

4 DSI接口仿真与测试

4.1 仿真平台及方案

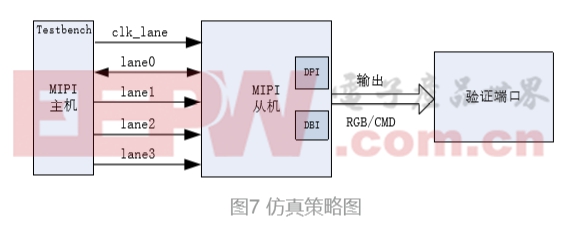

图7所示为此接口设计的仿真策略图,模拟MIPI主 机发送机制,通过数据通道发送高速数据,通过数据通 道0发送低功耗数据,该设计作为MIPI从机,接收数据 后进行编解码,最终将相应的数据和命令输出,通过观 察验证端口的仿真波形或数据比对,来确定设计是否完 成对应的功能要求。

4.2仿真结果及分析

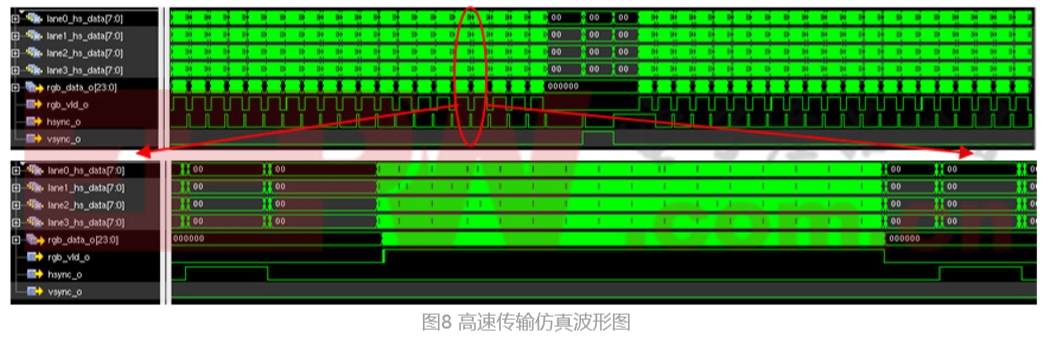

运行仿真后得到如图8所示的波形图,可以看出4个 通道都支持高速数据传输模式,能将接收到串行数据转为并行数据,从数据包中解码出图像数据信息,如RGB 数据、数据有效信号、行同步信号、帧同步信号等,符 合设计的功能要求,高速功能通过验证。其他功能也是 同理进行验证,不再赘述。

4.3 FPGA原型验证

在芯片流片前需要进行FPGA原型验证,将ASIC代 码移植到FPGA上,进行硬件上的验证,这样更接近芯 片实际情况,本质上模拟芯片的实际性能和应用,通过 FPGA快速实现硬件模块,缩短开发时间,提高开发的 效率,同时可以降低流片的风险和成本,所以也是芯片 设计中的重要流程。如图9为FPGA言行验证的平台,由 MIPI主机、转接板、连接线、FPGA开发板等组成,验 证通过后进行流片。

5 结语

本文介绍了一种基于MIPI协议,且应用于高分辨率 微显示驱动的接口设计,该接口设计采用了四通道的数据差分数据通道和1对 高速差分时钟通道。首先介绍了微显示和MIPI接口的研 究必要性,接着介绍了MIPI DSI协议,之后着重讲述了 MIPI DSI接口设计的工作原理,以及设计的系统方案、 主要模块的工作流程,最后介绍了仿真和FPGA验证的过 程及结果分析。支持高速传输模式、Escape模式、TA反 向传输模式,在低功耗模式下传输速率10 Mbit/s,高速 数据传输速率可达到900 Mbit/s。目前已完成设计,并经 过反复的仿真和验证,达到了设计要求,已完成流片。

参考文献:

[1] 季渊. 超还原硅基有机发光微显示器研究[D].上海:上海大学, 2012.

[2] 谭振平,黄嵩人.应用于LCOS显示芯片的MIPI DSI驱动接口IP 设计[J].科技传播,2016,8(03):78-79.

[3] 谭振平. 基于MIPI协议的显示驱动接口设计[D].湘潭:湘潭大学, 2016.

[4] 温浪明. 基于MIPI-DSI协议的LCD驱动接口设计[D].广州:华 南理工大学,2011.

[5] 郑杰. 一种适用于全高清显示的MIPI DSI接口设计[D].成都:电 子科技大学,2015.

[6] MIPI Alliance Specification for Display Serial Interface version 1.01.00[S].MIPI Alliance,2008.

[7] MIPI Alliance Specification for D-PHY version 1.2[S]. MIPI Alliance,2014.

[8] 苏晓峰.基于MIPI规范的LCD驱动接口设计 [D].广州:华南理工大学,2011.

本文来源于科技期刊《电子产品世界》2020年第03期第55页,欢迎您写论文时引用,并注明出处。

评论