带有分布式锁相环的相控阵的系统级LO相位噪声模型

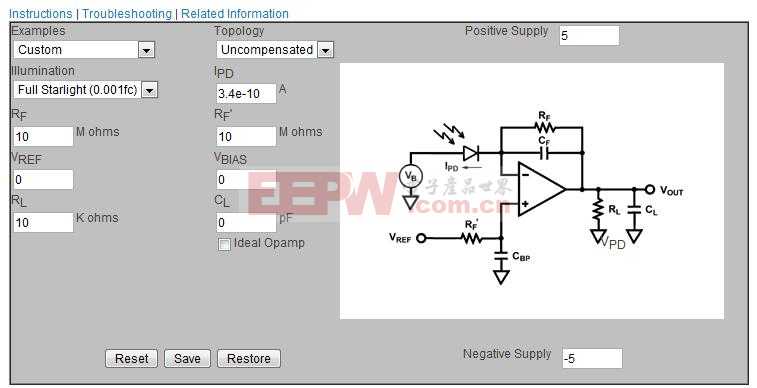

宽带PLL假设采用S波段标称频率,设置采用1 MHz环路带宽(尽量与实际环路的带宽一般宽),以进行快速调谐。

本文引用地址:http://www.eepw.com.cn/article/201903/398832.htm值得注意的是,选择这些模型是为了代表可能的实际情况,且说明了阵列中的累积效应。任何详细的设计或许都能够改善特定的PLL噪声曲线,这在预料之中,且这种分析方法旨在帮助从工程角度去决定应将设计资源分配在哪些位置以获得最佳总体效果,而不是为了做出相对于可用组件的确切论断。

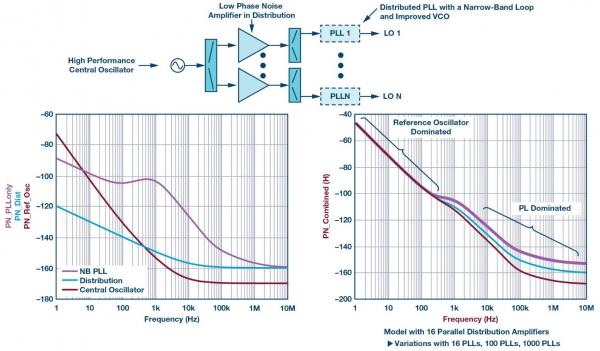

图5右下角的图计算了LO分布的总组合相位噪声。其中应用了各个贡献因素的PLL噪声传递函数,它们都被调整至输出频率,也包含PLL环路带宽的影响。系统数量也包括在内,并且假设它们是不相关的,因此,这个贡献减少了10logN。假设分布数量为16,如前所述,分布贡献会减少10log16。在实践中,随着分布不断重复,这种贡献会进一步减少。但是,额外的噪声贡献不那么显著。对于大型阵列中的扇出分布,噪声将由第一组有源器件主导。在16组扇出的情况下,如果每个有源器件都是16个其他有源器件的输入,那么在所有器件互不相关的情况下,16个器件的额外分布层只会降低~0.25 dB。如果继续这种分布,总体贡献将更小。因此,为了简化分析,不会考虑这种影响,且分布的噪声贡献通过计算前16个并行分布组件得出。

所得的曲线说明了几种效果。与单个PLL模型相似,近载波噪声由基准频率主导,远载波噪声由VCO主导,且在将不相关的VCO组合起来时,远载波噪声得到改善。这一点相当直观。不太直观的是,模型的值在由分布中的选择主导的偏移频率中占较大比重。这一结果导致考虑具有更低噪声分布和更窄PLL环路带宽的第二个示例。

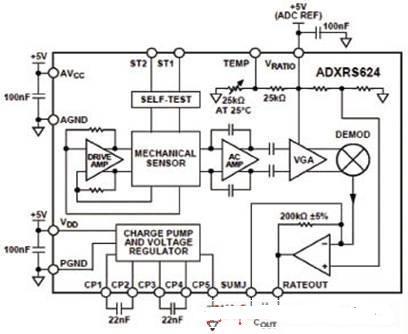

图6.分布式窄带PLL,分布中具备放大器。

图6显示了一种不同的方法。采用相同的低噪声晶体振荡器作为参考。但通过RF放大器来分配,而不是通过PLL重定时和重新同步。选择固定频率的分布式PLL。这会产生两种效果:采用单个频率且调谐范围较窄时,VCO本质上可以更好,且环路带宽可以变得更窄。左下角的图显示了各个贡献因素。中央振荡器与前一个例子相同。请注意分布放大器:考虑低相位噪声放大器时,它们的性能不是特别高,但比起使用PLL LC(如之前的示例)要好得多。VCO更好、环路带宽更窄时,分布式PLL在更高偏移频率下会得到改善,但在~1 kHz的中间频率下时,实际上要比宽带PLL示例差。右下角显示组合结果:参考振荡器主导低频,而高于环路带宽时,性能会由分布式PLL主导,且随着分布式PLL的阵列尺寸和数量增加而提高。

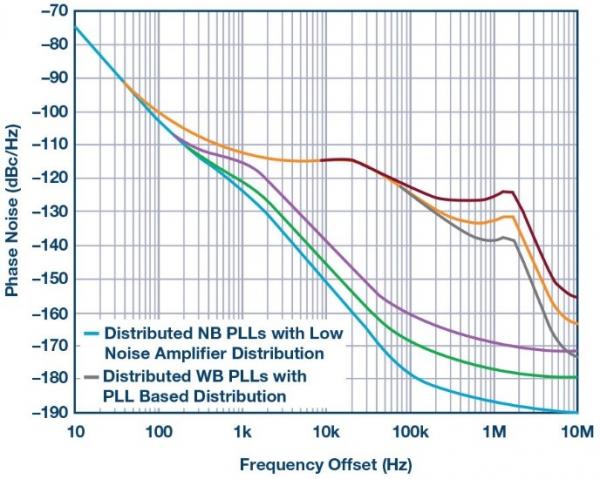

图7显示这两个示例之间的比较。注意~2 kHz到5 kHz偏移频率范围内的大范围差异。

图7.图5和图6之间的比较,显示了基于所选的分布和架构的广泛系统级性能范围。

分布式PLL阵列级考虑因素

基于对总体系统相位噪声性能的加权贡献的理解,可以得出几个与相控阵或多通道RF系统架构相关的结论。

PLL带宽

针对相位噪声优化的传统锁相环设计将环路带宽设置为偏移频率,以最小化总体相位噪声曲线。此时的频率一般是参考振荡器相位噪声按输出频率标准化后与VCO相位噪声相交的频率。对于具有多个锁相环的分布式系统,这可能不是最佳环路带宽。分布式组件的数量也需要考虑。

要在采用分布式锁相环实现的系统中获得最佳LO噪声,需要采用一个较窄的环路带宽来最小化参考振荡器的相关噪声贡献。

对于需要快速调优PLL的系统,通常会扩大环路带宽来优化速度。遗憾的是,这种优化分布式相位噪声贡献的思路本身就是背道而驰的。克服这一问题的选择之一是在宽带环路之前设置分布式窄带清理环路,以降低参考噪声和分布噪声相关位置的偏移频率。

大型阵列

对于使用数千个通道的系统,如果分布式组件的贡献之间保持互不相关,则系统能够获得大幅改进。主要考虑的问题可能围绕参考振荡器的选择展开,以及面向分布式接收器和激励器维持低噪声分布系统。

直接采样系统

随着速度和RF输入带宽持续提升的GSPS转换器的不断普及,直接采样系统正逐渐在微波频率实现。这导致出现一种有趣的取舍现象。数据转换器只需要一个时钟频率,RF调谐完全在数字域中完成。通过限制调谐范围,可以构建具备相位噪声性能更高的VCO。这也使得创建数据转换器时钟的PLL的环路带宽降低。更低的环路带宽会将参考振荡器的噪声传递函数降至更低的偏移频率,从而减少它在系统中的贡献。这一点,再加上改进过的VCO,在某些情况下可能给分布式系统带来好处,即使单通道比较结果似乎更青睐替代架构:

组件选项

根据系统架构中所需的选择,设计人员拥有大量可用的组件选项。2018年度RF、微波和毫米波产品选型指南更新版现已发布。

近期的集成VCO/PLL选项包括ADF4371/ADF4372。它们提供的输出频率分别高达32 GHz和16 GHz,采用–234 dBc/Hz的先进PLL相位噪声FOM。ADF5610提供高达15 GHz的输出。ADF5355/ADF5356的输出可达13.6 GHz,ADF4356的输出可达6.8 GHz。

对于单独的PLL和VCO配置,ADF41513的工作频率可达26 GHz,且配有一个先进的锁相环相位噪声FOM,其相位噪声FOM为-234 dBc/Hz。有时,在选择PLL IC时要考虑的一个问题是在尽可能高的频率上操作鉴相器,从倍增20logN到输出频率,最小化环路中的噪声。HMC440、HMC4069、HMC698和HMC699采用的PFD的工作频率高达1.3 GHz。对于VCO,2018年选型指南列出了几十个VCO选项,范围从2 GHz到26 GHz不等。

对于直接采样选项,ADC和DAC均已发布。产品支持在L频段和S频段直接采样。ADC具有更高的输入频率带宽,支持C频段直接采样。AD9208是一个双通道3 GSPS ADC,输入频率为9 Ghz,支持在上Nyquist区采样。AD9213是一个单通道10 GSPS ADC,支持具有较大瞬时带宽的接收器。对于DAC, AD917x系列采用双通道12 GSPS DAC,AD916x系列采用单通道12 GSPS DAC,经过优化之后可实现更低的残留相位噪声和更好的SFDR。两个系列都支持L频段和S频段波形生成。

本节仅提供入门指南。频率更高、性能更好的新器件层出不穷。请访问我们的网站,或者联系本地销售支持团队获得最新的IC信息。

结语

本文介绍了为采用分布式锁相环的系统评估相位噪声的方法。该方法的前提是:每个组件都可以通过其各自的噪声、组件与系统输出之间的噪声传递函数、使用的数量以及器件之间的任何相关性来进行跟踪。所示的示例并不意在对可用的组件或架构功能进行论断。它们旨在说明一种方法,以帮助设计人员在数字波束成形相控阵中,对LO中的阵列级相位噪声贡献因素以及为分布式波形发生器和接收器提供服务的时钟分布网络进行有根据的评估。

参考文献

1 Ulrich Rohde,《微波和无线频率合成器:理论与设计》。Wiley,1995年。

2 Floyd Gardner,《锁相技术》。第三版,Wiley,2005年。

3 Dean Banerjee,《PLL性能、仿真和设计》,第四版。Dog Ear Publishing,2006年8月。

4 Dan Wolaver,《锁相环电路设计》。Prentice Hall,1991年2月。

5 Avi Brillant。“了解锁相DRO设计的各方各面。”Microwave Journal,2000年9月。

6 Peter Delos,“锁相环噪声传递函数”。High Frequency Electronics,2016年1月。

7 ADS PLL示例。“PLL相位噪声”。Keysight技术。

9 Ian Collins,“锁相环(PLL)基本原理”。《模拟对话》,2018年7月。

10 E.Anthony Nelson,“相控阵的噪声考虑因素”。IEEE,Telesystems会议,1991年。

11 Heng-Chia Chang,“面向波束控制有源相控阵、带有独立振荡器的耦合锁相环分析”。IEEE Transactions on Microwave Theory and Techniques,第52卷,第3期,2004年3月。

12 Thomas H?hne和Ville Ranki,“波束合成过程中的相位噪声”。IEEE Transactions on Wireless Communication,第9卷,第12期,2010年12月。

13 Antonio Puglielli、Greg LaCaille、Ali Niknejad、Gregory Wright、Borivoje Nikolic、Elad Alon,“OFDM多用户波束合成阵列中的相位噪声测量与跟踪”。IEEE ICC,无线通信研讨会,2016年5月。

作者简介

Peter Delos是ADI公司航空航天和防务部门的技术主管,在美国北卡罗莱纳州格林斯博罗工作。他于1990年获得美国弗吉尼亚理工大学电气工程学士学位,并于2004年获得美国新泽西理工学院电气工程硕士学位。Peter拥有超过25年的行业经验。其职业生涯的大部分时间花在高级RF/模拟系统的架构、PWB和IC设计上。他目前专注于面向相控阵应用的高性能接收器、波形发生器和合成器设计的小型化工作。

评论