人工智能 VS 芯片工程师

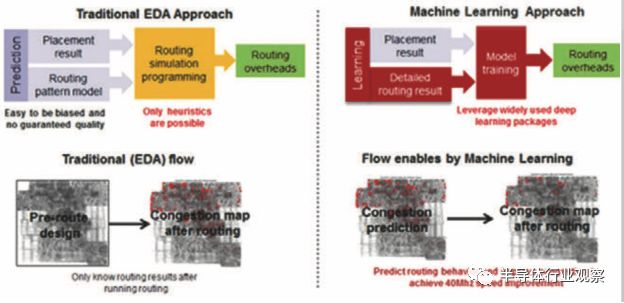

那么机器学习和人工智能如何帮助布局布线呢?

本文引用地址:http://www.eepw.com.cn/article/201902/397478.htm事实上,这里的机器学习的帮助主要来自于从大数据中的学习能力。传统的启发式算法本质上并未考虑算法应用的具体语境,每次在探索的过程中理论上会以等概率去探索各种方向。虽然在长达数十年的工程实践中,人们会在布线的启发式算法中加入各种优化,但是人类工程师对于布线这个高维度的复杂问题的把握程度毕竟有限。举例来说,当运行布线的时候发现本地布线非常拥挤,而右边若干距离的地方布线较为宽松,那么应该把多少本地走线移动到右边?

如果移动过少难以完全缓解布线拥挤问题,而移动过多无非就是把本地的拥挤移动到了右边,也并非最优。这种变量维度过高的问题对于人类是很难把握的,而机器学习则可以从大量布局布线的实际案例中去学习如何最优化启发式算法的探索过程,从而使布线过程优化结果更好,同时也能减少探索次数,也就是减低了算法运行时间。Cadence在去年宣布已经在布局布线引擎中加入了机器学习的元素,其结果是能够将运行结果的total negative slack改善15%,这可以说是一个很不错的起步。

在布局布线领域,人工智能的另一个重要应用就是能为流程加入预测能力,从而减少迭代次数。众所周知,数字电路布局布线是一个反复迭代的过程,流程前后的环节会互相影响。布局的过程会影响布线的结果,而如果布线的结果太差又会导致工程师去再次优化布局以获得改善。这样的反复迭代流程显然会对设计时间带来影响,那么能否在布局的时候就去预测其对于布线的影响,从而不要等到真的布线结果出来之后再去优化布局呢?

之前也有不少尝试,而使用机器学习通过学习大量的布局和布线拥挤程度之间的关系去做预测可以大大提升预测的精准度,从而减少迭代次数。在ISSCC 2017,台积电的研发副总裁Cliff Hou就在其演讲中重点介绍了这种基于机器学习的后端设计方法,并认为它将会为未来的集成电路研发带来更多效率提升。

人工智能与电路设计师

在之前的分析中,我们可以看到目前人工智能的主要优势还是在于高维数据的处理和定量统计分析能力。这一波的人工智能在抽象推理方面仍然较弱,因此难以全面胜任复杂的设计任务。我们人类在处理复杂设计的任务时,普遍的方法是将其降维处理,分解成多个较简单的子任务并分而治之,当子任务全部都完成时复杂的设计任务自然就完成了。而人工智能目前尚缺乏这种自适应将复杂任务分而治之的分解能力。

如果说这种从复杂的客观中抽象出简单的规律的能力称之为“降维”,而从复杂世界中把握高维数据之间的复杂关系的能力就可以说是“升维”了。人类的降维能力较强,而人工智能的升维能力较强,因此人类与人工智能最好的合作方法就是人类负责降维,抽象出设计框架,并将复杂的设计分解成较简单的子任务,而人工智能则在每个子任务中充分探索高维设计空间,帮助完成最优化设计。

从这种意义上来说,人工智能在短期内并不会替代真人工程师,而是会在设计流程中帮助提升效率,减少算法和设计流程层面上不必要的迭代,而这一切对于真人设计师来说都是好事。因此,我们认为,人工智能将会是电路工程师的好朋友。

评论