如何通过电源去耦来保持电源进入集成电路(IC)的各点的低阻抗?

◀ 适当的局部去耦在PCB上是必不可少的

本文引用地址:http://www.eepw.com.cn/article/201811/394038.htm典型的4层PCB通常设计为接地层、电源层、顶部信号层和底部信号层。表面贴装IC的接地引脚通过引脚上的过孔直接连接到接地层,从而最大限度地减少接地连接中的无用阻抗。

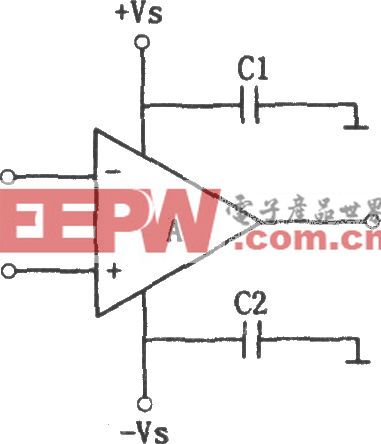

电源轨通常位于电源层,并且路由到IC的各种电源引脚。显示电源和接地连接的简单IC模型如图2所示。

图2. 显示走线阻抗和局部去耦电容的IC模型

IC内产生的电流表示为IT。流过走线阻抗Z的电流产生电源电压VS的变化。如上所述,根据IC的PSR,这会产生各种类型的性能降低。

通过使用尽可能短的连接,将适当类型的局部去耦电容直接连接到电源引脚和接地层之间,可以最大限度地降低对功率噪声和纹波的灵敏度。去耦电容用作瞬态电流的电荷库,并将其直接分流到地,从而在IC上保持恒定的电源电压。虽然回路电流路径通过接地层,但由于接地层阻抗较低,回路电流一般不会产生明显的误差电压。

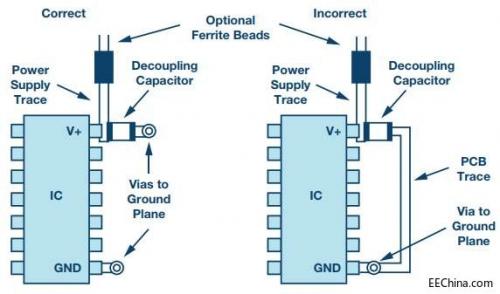

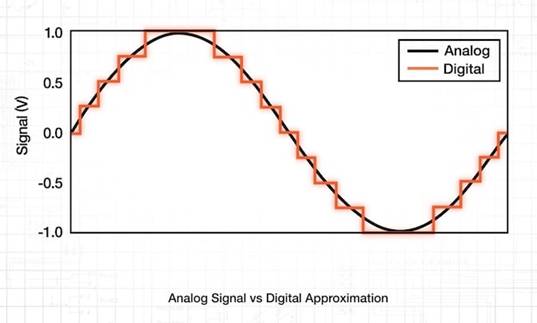

图3显示了高频去耦电容必须尽可能靠近芯片的情况。否则,连接走线的电感将对去耦的有效性产生不利影响。

图3. 高频去耦电容的正确和错误放置

图3左侧,电源引脚和接地连接都可能短,所以是最有效的配置。然而在图3右侧中,PCB走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

◀ 选择正确类型的去耦电容

低频噪声去耦通常需要用电解电容(典型值为1μF至100μF),以此作为低频瞬态电流的电荷库。将低电感表面贴装陶瓷电容(典型值为0.01μF至0.1μF)直接连接到IC电源引脚,可最大程度地抑制高频电源噪声。所有去耦电容必须直接连接到低电感接地层才有效。此连接需要短走线或过孔,以便将额外串联电感降至最低。

大多数IC数据手册在应用部分说明了推荐的电源去耦电路,用户应始终遵循这些建议,以确保器件正常工作。

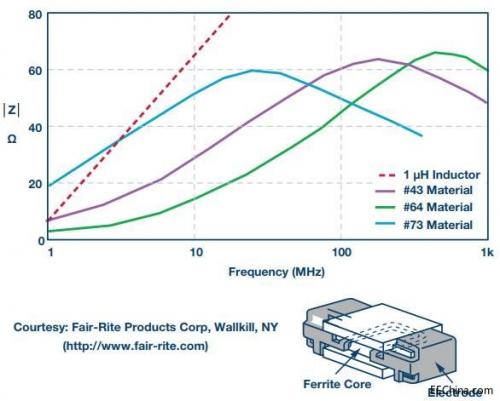

铁氧体磁珠(以镍、锌、锰的氧化物或其他化合物制造的绝缘陶瓷)也可用于在电源滤波器中去耦。铁氧体在低频下(<100kHz)为感性—因此对低通LC去耦滤波器有用。100kHz以上,铁氧体成阻性(低Q)。铁氧体阻抗与材料、工作频率范围、直流偏置电流、匝数、尺寸、形状和温度成函数关系。

铁氧体磁珠并非始终必要,但可以增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会饱和,特别是在运算放大器驱动高输出电流时。当铁氧体饱和时,它就会变为非线性,失去滤波特性。

请注意,某些铁氧体甚至可能在完全饱和前就是非线性。因此,如果需要功率级,以低失真输出工作,当原型在此饱和区域附近工作时,应检查其中的铁氧体。典型铁氧体磁珠阻抗如图4所示。

图4. 铁氧体磁珠的阻抗

在为去耦应用选择合适的类型时,需要仔细考虑由于寄生电阻和电感产生的非理想电容性能。

评论