从GDDR1到GDDR6的详细资料都在这里

QDR是什么?

本文引用地址:http://www.eepw.com.cn/article/201811/393906.htmSDR(Single Data Rate):单倍数据倍率,只利用时钟信号的上沿传输数据,例如SDRAM等。

DDR(Double Data Rate):双倍数据倍率,利用时钟信号的上沿&下沿传输数据,例如DDR-SDRAM等。

QDR(Quad Data Rate):四倍数据倍率,在DDR的基础上,拥有独立的写接口和读接口,以此达到4倍速率,例如QDR-SRAM等 。DDR2-SDRAM,DDR3-SDRAM基本原理和DDR-SDRAM是一样的,通过提高时钟频率来提升性能,因为时钟频率提高了,必须做相应的预处理(DDR支持2、4、8busrt, DDR2支持4和8,而DDR3只支持8)。

QDR是Quad Data RateStatic Random Access Memory(QDR SRAM)的缩写,也就是四倍数据速率静态随机存取存储器的意思。QDR的四倍数据速率是相对普通SRAM而言的。

普通SRAM使用半双工总线,即在同一时刻只能进行读或者写操作(读/写共用一条数据通道),所以普通SRAM又称作SDR(Single Data Rate)SRAM,即“单倍数据速率静态随机存取存储器”。

DDR(Double Data Rate) SRAM在SDR SRAM的基础上做了改进,与SDR SRAM只在参考时钟的上升沿采样数据不同,DDR SRAM在参考时钟的上升沿和下降沿都采样数据,这样,DDR SRAM在一个时钟周期内可以传输双倍数据,DDR SRAM(双倍数据速率SRAM)也是由此得名的。

QDR在保留DDR特征的基础上,对其数据总线进行了升级,DDR只有一条数据通道,数据读/写操作共用,属于半双工工作方式,而QDR拥有两独立条数据通道,数据读/写操作可以同时进行,属于全双工工作方式,因此,QDR的数据存取速率又是DDR的两倍。

这样计算下来,QDR的数据存取速率是SDR的四倍,四倍数据速率的雅称也因此而来。QDR1/2/3的最高工作频率分别为200/333/500MHz。在高速通信系统中(40G/100G)基本上都使用QDR。

QDR器件规范是由Cypress、IDT、NEC、Samsung和Renesas等公司组成的QDR联盟共同定义和开发的。QDR联盟的官方网站是:http://www.qdrsram.com。

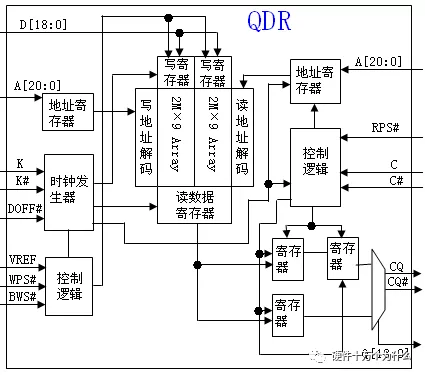

同DDR一样,QDR也分为QDR1、QDR2和QDR3。与QDR1相比,QDR2增加了一对源同步时钟,可以帮组SRAM控制器捕获数据,此时钟被称为反馈时钟(CQ和CQ#),这个反馈时钟与QDR2的输入参考时钟保持同步,同时又与QDR2输出路径的数据总线保持沿对齐。这样,QDR2产生的整体数据有效视窗便会比同频率的QDR1增大约35%,而延迟却比QDR1少了二分之一个周期,这额外的半周期可容许在最低的延迟下进行更高频率和更大带宽操作。QDR3目前还处在概念中,QDR联盟于2004年5月制定的QDR3规范中,器件的最高时钟频率可达500MHz。QDR器件结构示意图如下所示:

4K@,H9]lz0

1).K/K#:QDR系统时钟信号;

2).C/C#:读端口输入时钟;

3).CQ/CQ#:输出环回时钟;

这里说明下,K/K#、C/C#和CQ/CQ#不是真正的差分信号,而是相位相差180度的伪差分时钟,在测试时不能使用差分探头,一般使用两个单端探头。

4).A[20:0]:地址输入信号,读写通道复用,分别在时钟K/K#的上升沿采样;

5).WPS#:写端口选择输入信号,在时钟信号K的上升沿有效,当WPS#无效时,写端口信号被忽略;

6).BWS[3:0]#:比特写入选择信号,用于选择将拿个Byte写入到QDR钟,对于9位数据位宽的QDR,用BWS0#控制,对于18位数据位宽的QDR,由BWS0#控制低9位,BWS1#控制高9位,其他以此类推;

7).NWS[0:1]#:4字节写入选择信号(此管脚只在8位QDR器件上才有),用来控制当前写端口的哪4位字节被写入,NWS0#控制D[3:0],NWS1#控制D[7:4]。

8).RPS#:写端口地址选择输入信号,时钟K上升沿有效,当RPS#信号无效时,读端口信号被忽略;

9).D[18:0]:写操作数据输入通道,在时钟K和K#的上升沿有效;

10).Q[18:0]:读操作数据输出通道,单时钟模式下,在在时钟K和K#的上升沿有效,多时钟模式下,在时钟C和C#的上升沿有效;

11).ZQ:输出阻抗控制信号。用于控制QDR的输出端口的CQ/CQ#以及Q[18:0]等信号的输出阻抗。当ZQ和GND间的电阻为RQ时,则CQ/CQ#和Q[18:0]的输出阻抗被设置为0.2RQ。当ZQ直接连接到VDD时,输出信号有最小的输出阻抗,ZQ不能悬空或直接接地;

12).DOFF#:DLL使能输入信号,当该管脚接地时,将会关掉QDR内置的DLL;

13).144M/288M:144M/288M地址扩展引脚,在72M器件上,这些管脚必须拉低。

QDR SRAM的I/O端口采用的是HSTL电平。HSTL即High SpeedTransceiver Logic,是一种基于EIA/JESD8-6标准的数字接口电路逻辑,其输出为一差分放大器(如果只使用一端的话,另一端需要与内部参考电压相连),QDR具有单独的输出端口电源Vddq,QDR1为2.5V、QDR2为1.8V、QDR3为1.2V。

QDR有三对参考时钟,其中,只有K/K#时钟是必须的,它是写数据和地址信号的采样时钟。C/C#和CQ/CQ#这两对时钟可选,QDR有四种时钟设计方案,分别如下:

1).仅使用K/K#时钟。K/K#既是写参考时钟,也是读参考时钟;

2).用K/K#时钟和C/C#时钟,不使用CQ/CQ#时钟;

3).用K/K#时钟和C/C#时钟的换回环,不用CQ/CQ#时钟;

4).用K/K#时钟和CQ/CQ#时钟。

由于K/K#时钟和CQ/CQ#时钟分别是由QDR控制器和QDR本身提供的,这样,在读写时都有源同步时钟做参考,所以,在高速设计中,基本上都是使用第四种时钟方案。

使用单时钟模式时,C/C#时钟必须从外部上拉到高电平(CQ/CQ#是输出时钟,无需处理),在使用第二种时钟模式时,C/C#的时钟的PCB走线必需要比K/K#时钟长,QDR2 SRAM有一个参数tKHCH(即K/K#时钟和C/C#时钟的skew),规范中要求此参数必须大于0,因为QDR的同时读写特点,假设在同一时钟周期内,要对同一个地址的数据进行读操作和写操作,规范要求是,要先进行写操作,后进行读操作,也就是写参考时钟K/K#需要比读参考时钟C/C#先到达。但是,规范中同时规定,C/C#时钟与K/K#时钟之间的skew必须小于三分之一时钟周期。

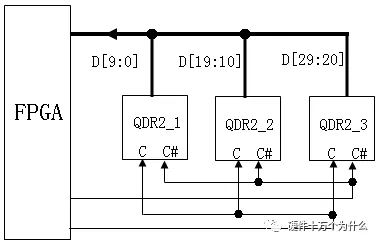

如果将多片QDR2 SRAM器件并联使用的话,需要注意C/C#时钟的PCB走线方式,即C/C#时钟须先到达最远端的QDR器件(即第三种时钟方案),最后到达最近处的QDR器件,这样,参考时钟信号的延迟正好可以抵消数据信号的延迟,确保几个器件上的数据保持同步,如下图所示。

使用QDR器件时,须注意一下几点:

1).QDR2有最低频率要求,最低工作频率不能低于120MHz;

2).QDR上电期间,要保证DOFF#管脚一直处于低电平,因为DOFF#的作用是使能器件内部的DLL,在刚上电的这段时间,时钟信号本身是不稳定的,为了让内部DLL正确的锁住时钟,需要停止时钟信号至少30ns来复位内部DLL,然后等外部时钟稳定后在使能DLL去锁定稳定的时钟;

3).VDD要先于VDDQ上电,VDDQ要先于VREF或与之同时上电。

评论