PEMFC控制系统电源的设计

实际取10匝。

对24 V输出:

实际取42匝。

2.3 整流滤波

(1)输出滤波电感的设计。输出滤波电感中的电流除存在直流分量外,并且叠加一个较小的交流分量。输出滤波电感的设计一般要求电感电流的最大脉动量为最大输出电流的10%~20%。

对于输出电压Vo=5 V,输出电流Iomax=1 A,最大占空比Dmax=0.63。

代入这些值则得:L=462.5μH。

对于输出电压Vo=24 V,重复上面的计算可得:L=0.004 4 H。

(2)输出滤波电容的选择。输出滤波电容上的纹波电流:

根据上一节得到的数据,将ISRMS1=1.712 A,ISRMS2=0.856 A分别代入上式中,可求得Iri11.39 A,Iri2=0.695 A。滤波电容在20 kHz时的纹波电流应大于等于Iri。

输出的纹波电压由式Vri=IsprO决定。滤波电容C2,C3,C4选用330μF/50 V,C5选用100 μF/25 V。

3 控制电路的设计

3.1 PWM控制电路

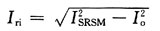

这里以数字信号处理器(DSP)TMS320LF2407为核心,设计了全数字PWM控制系统,如图3所示,具有更好的实时性,能很好的适应PEMFC发电机的输出特性。

输出电压经霍尔电压传感器隔离采样后送到DSP的ADC模块进行模数转换,这些值在一定时间内经过一系列数字PI控制后,给全比较单元产生一个新的比较值,该比较值将在下一个开关周期改变PWM波形的占空比,这样就达到了控制输出电压为所要求值的目的。

DSP中并没有自动生成PWM信号的功能,要通过编程的方法实现它,通过一个单比较1的输出脚PWM1实现所需要的PWM信号,下面具体介绍这种方法。单比较单元有一个比较寄存器,用来存储比较值,当计数器于比较值相等时,相应的PWM输出引脚电平发生跳变,怎样跳变取决于PWM引脚的工作方式。

PWM输出脚工作方式:有效高方式,有效低方式等。在定时器1工作在连续增减计数时,电平的为:输出脚若设置为有效高,计数器为零时,输出脚电平为零,计数器开始增计数,当与比较值相等时,这时输出脚为有效状态,电平变高。计数器到达周期值后,开始减计数,当减计数到比较值时,输出脚为无效状态,电平变低。输出脚若设置为有效低。则此时的电平变化与有效高状态正好相反。本文采用有效高工作方式。

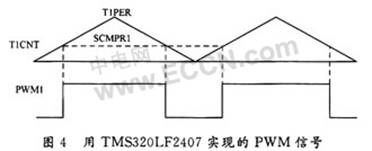

T1CNT为计数器1的计数值,T1PER为计数器l的周期值。当T1CNT的值增加到与T1PER相等时,计数器1开始减计数,当T1CNT的值减到0时,计数器增计数。计数器值随时间变化如图4所示。在计数器的计数值与各比较单元的比较寄存器值(SCMPRl)相等时,输出脚电平发生变化。波形图如图4所示,从图中可以看出,计数器值通过与实时变化的比较寄存器值(SCMPR1)相比较,可以调节PWM脉冲宽度,进而改变功率管的占空比,达到对DC/DC变换器输出电压的实时控制。

评论