断电还是关断?

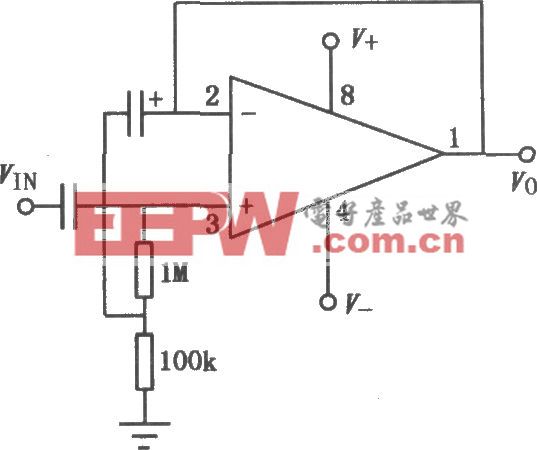

所有这些影响使得关断模式对现代器件越来越有吸引力。 现代芯片充盈着各种特性,包括成百上千万的元件;如果保持开启,每个器件都可能产生漏电流。 优化特性使用并关断芯片中不使用的部分,可以消除其中的大部分漏电流。 然而用户应该确保供应商明确支持这些模式,而不要试图自行开发关断功能。

更多情形

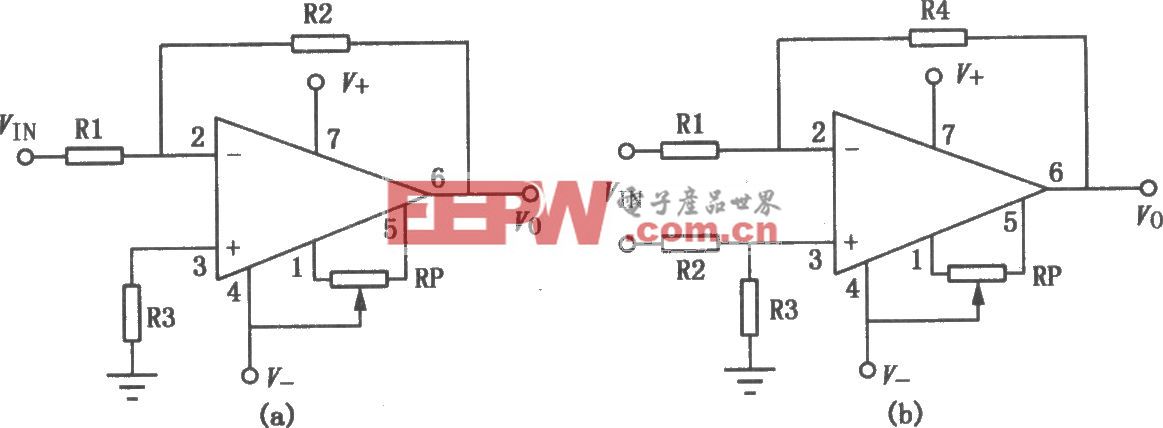

关于关断的完整拼图还缺几片。 如果同时切断接地连接(这将形成另一条低阻抗路径)会怎样? 这与直接驱动I/O引脚而不使能电源的ESD情况相似,如果信号足够强,可能会触发ESD保护结构,导致高电流流经其他相连的I/O引脚,产生假上电情况。 更有可能的情况是信号稍弱一点,但仍然强到足以通过一条路径(如I/O箝位)抵达电源。 信号可能无法触发电源箝位,但会在电源上引起意想不到的虚电压,从而造成未知工作状态,具体情形取决于芯片的拓扑结构。 任一情况下,如果电路状态持续如此,则芯片可能受损,除非前一级已经停止供应高电流。 如果信号强度不足以触发I/O箝位,它仍可能会对所遇到的第一个晶体管施压,长时间操作后可能会损坏该晶体管。

如果断开电源并拉低电源输入呢? 这种情况下,芯片无浮动电源,不可能触发任何ESD结构,但PMOS漏极电压可能高于主体电压,使漏极-主体二极管正偏。 这样,来自前一级的电流将经过PMOS器件流至地,直至器件烧毁、前一级停止提供电流或设计人员注意到报警。

结论

关断模式使得系统级响应更快速、更安全,因而是不可缺少的特性,尤其是在考察复杂系统中的完整信号链时。 如果器件之间的交互很有限,或者系统整体很简单,足以确保不会出现复杂情况,则可以考虑完全切断电源。

评论