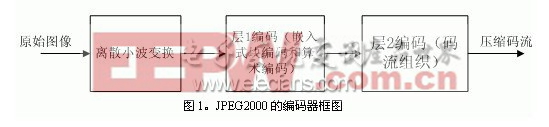

如何用JPEG2000中位平面编码设计存储优化方案?

if (gene_layer_fin) nstate = fill_ram;else nstate = gene_layer;end

fill_ram:begin

。。。gene_layer_en = 0;fill_ram_en = 1;pass_judge_en = 0; 。。。

if (fill_ram_fin) nstate = pass_judge;else nstate = fill_ram;end

。。。

endcase

5.实验结果

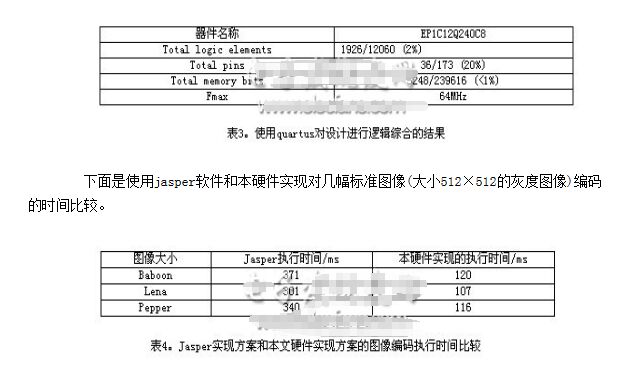

本设计采用modelsim工具进行了功能仿真,使用quartus[6]工具进行了逻辑综合,得到的综合结果如表3所示。

6.结论

本文通过对JPEG2000中的位平面编码器的存储方案进行了分析,设计了一个高效的存储结构以及相应的控制电路,设计采用verilog[4]语言描述,通过quartus[6]软件逻辑综合后,能够在0.1s内完成一幅512×512灰度图像的编码,编码时间仅为jasper[3]软件实现方案的 30%左右。由于块编码器的特点,每个码块的编码本身是独立的,可以并行进行,而且根据综合结果,使用EP1C12Q240C8完全可以在一块芯片内集成多个位平面编码器的IP核,每个块编码器核可以并行执行,因此,可以进一步提高编码器的速度,从而使实时处理图像成为可能。另外,还可以将设计定制为 ASIC,将最终产品应用到数码相机、图像监控中,其市场前景是十分广阔的。

评论