盘点RS485收发连接器参考电路设计

555定时器为边沿触发,当TxD发送高电平时,555定时器OUT引脚输出低电平,当TxD发送低电平时,555定时器OUT引脚输出高电平,当TxD转为高电平时,OUT引脚输出的高电平状态会延迟一会再转入低电平,以确保发送数据的正确性。

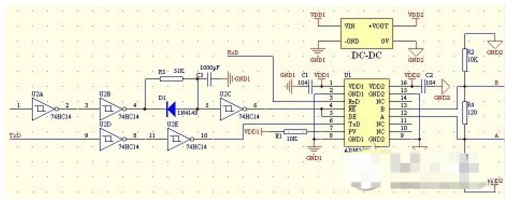

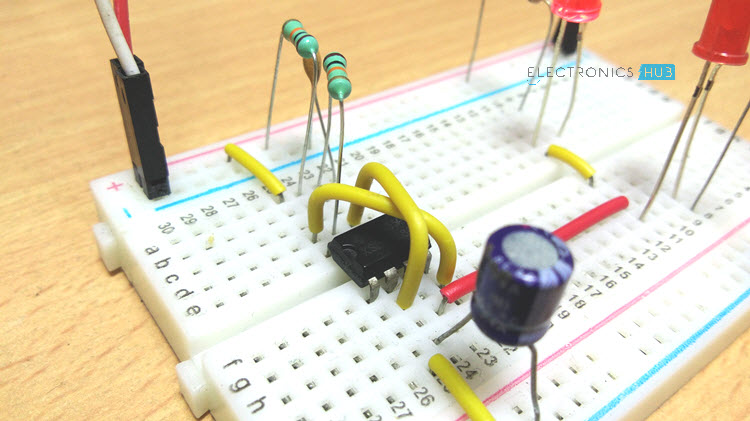

采用74HC14和RC电路实现,此电路是对单纯使用74HC14实现自收发电路的改进,增加了RC充放电电路,减少总线处于空闲状态的时间,电路如下图:

当TxD信号为高电平,则通过电阻为电容充电,其充电时间为T,该时间应设置为串口发送一个字节所需要的时间,由R,C参数来确定。当电容充满后,则DE/RE为低电平,使ADM2483处于接收状态。在发送数据时,TxD起始位产生第一个下降沿,使电容经过二极管进行快速放电,使DE/RE很快变为高电平,ADM2483处于发送状态。在发送过程中, 当TxD变成高电平时,电容通过电阻缓慢充电,使DE/RE仍然保持在发送状态,可有效吸收总线上的反射信号。当RC充电结束,使DE/RE转入接受状态时, 总线上的上拉、下拉电阻将维持TxD高电平的发送状态,直至整个bit发送结束。

当数据发送完毕以后,TxD变为高电平,RC又开始充电,即经T时间后,ADM2483又转换为接收状态。以上所有电路均为参考电路,为电路设计者提供思路,在实际使用中请再次验证,以确保电路的稳定及不会对系统造成破坏。对于电路损坏造成的损失,概不负责。

评论