4 种有源滤波器设计工具详细评估

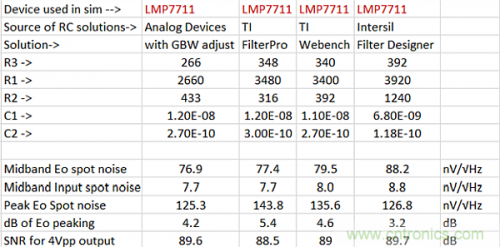

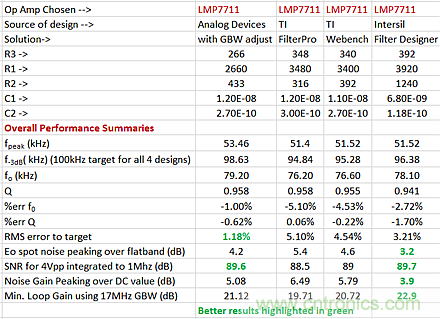

一种查看积分噪声的方法是使SNR形成特定的预期最大Vpp输出。这些设计示例还会针对SNR进行仿真,并使用4Vpp最大输出的假定(在TINA的噪声面板中输入1.414Vrms的4Vpp RMS值)积分到1MHz。表3总结了使用4种设计的噪声仿真结果。

本文引用地址:http://www.eepw.com.cn/article/201807/389496.htm

表3:噪声仿真结果

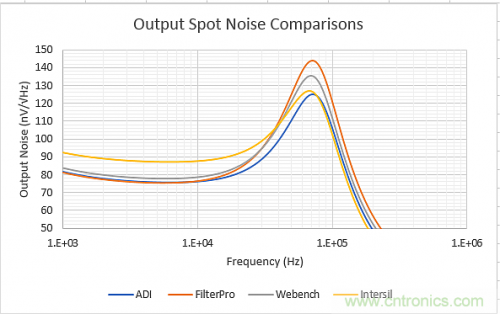

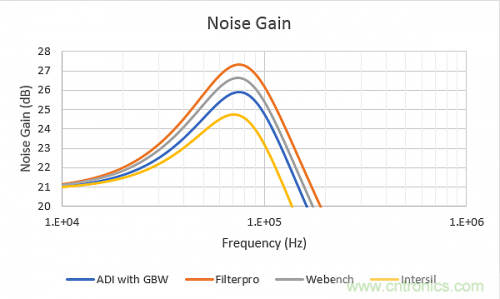

图5是使用LMP7711 TINA模型对表3中4组RC值示例仿真得到的输出点噪声与频率关系图。

图5:输出点噪声仿真比较

观察图5的噪声图,得到下面的结论:

Intersil值给出了最高的平带噪声(最高电阻值),但在该水平上峰值最低;

其它3种设计的平带噪声几乎相同,其中ADI设计的峰值最小;

FilterPro设计的峰值最高,原因是输入电阻大于回路内电阻;

平带内的输入参考噪声并非远大于LMP7711模型+602Ω噪声的5.9nV/Hz。这表明电阻已被调整到只会轻微影响总体结果的范围。R2/R3比率(以及由此产生的噪声增益零点位置)的差异对积分噪声和相应的SNR有更大影响;

ADI和Intersil的RC方案的信噪比,比FilterPro设计要好1dB以上。这是因为与其它三种方案相比,FilterPro设计的噪声增益零点展得更宽了。这些差异是由于RC方案全都针对相同的滤波器响应形状。

噪声增益(NG)峰值和环路增益(LG)分析

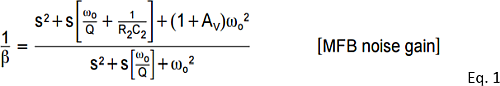

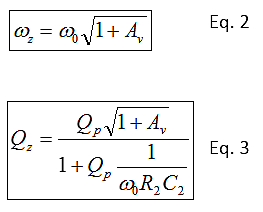

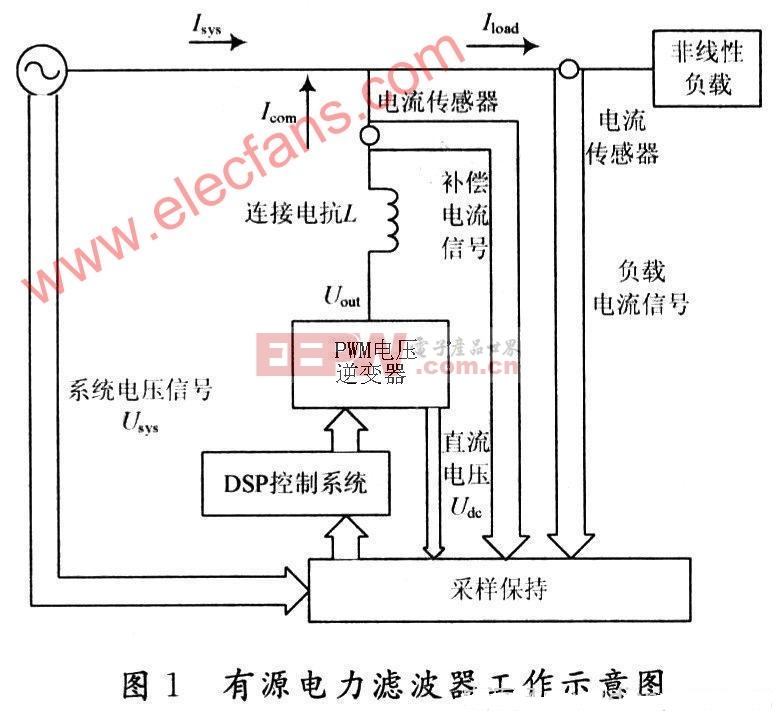

MFB拓扑固有的噪声增益频率响应随着频率的变化达到峰值。峰值的产生归因于期望的频率响应极点和噪声增益零点——它们被控制产生或多或少的带内峰值,同时仍能提供期望的闭环响应形状。图1电路的MFB噪声增益由公式1给出,公式的分子(用于求解传递函数零点)是尽可能根据目标响应形状而写出。

除了内环中的1/(R2C2)积分环节外,分子完全受到期望的滤波器极点所限制。这表明可以使用积分环节比例,在一定限度范围内移动零点。MFB噪声增益的零点总是实数,但可以用熟悉的、类似于公式1中分母的ωz和Qz格式来描述。Qz总是 < 0.5,表明有2个实零点。为得到ωz和Qz以及零点,求解公式1的分子部分,得到公式2和3,它们根据期望的有源滤波器极点ω0和Qp来写出。

零点落在期望的滤波器f0的上方和下方,将Qz增加到0.5将使下面的零点频率上升。这样可以随频率降低峰值噪声增益,为任何所选运放增加通带LG。

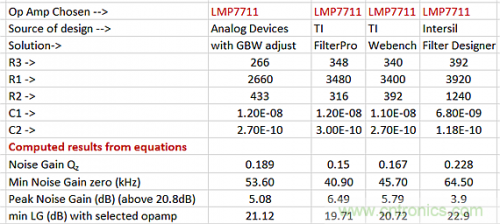

表3中的每种方案都可以使用公式1对NG形状进行分析,使用公式3得出Qz,并解出较低噪声增益零点。然后使用公式1可以为表3中的不同RC方案生成不同NG与频率关系曲线,如图6所示。这表明所有针对相同闭环响应的方案在峰值NG上有巨大差异。

图6:表3中不同RC方案的噪声增益响应形状

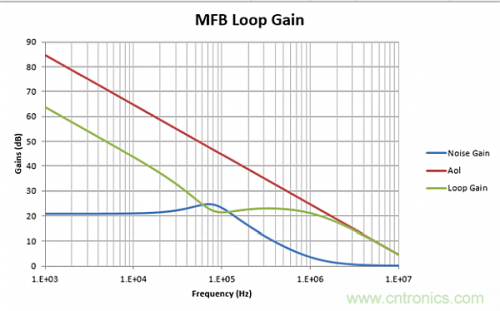

将NG曲线与LMP7711的Aol曲线结合,并产生差值作为LG,可以得到最小环路增益。图7中的示例计算了表3中Intersil RC方案的噪声增益,显示了LMP7711的17MHz Aol曲线,以及相应的LG。

图7:表3中Intersil RC值的噪声增益和所得环路增益以及LMP7711 Aol

所有二阶低通MFB LG图都表现出与图6相似的特征。关键点包括:

LMP7711的Aol曲线使用17MHz GBW。从40dB增益线上看,它穿过170kHz并乘以100倍可以看出;

NG曲线显示了f0附近的峰值特性。在这种情况下,对于表3中使用Intersil RC值的设计示例,其峰值降低了(如图6所示);

对于期望的滤波器形状,当NG跌落到f-3dB以上时,LG在接近最大噪声增益处达到最小值,且在从此处到约10倍f-3dB频率的范围内保持相对平坦;

NG因设计中的反馈电容,在较高频率处接近0dB(1V/V)。这表明需要有单位增益稳定的运放,解决这个约束的方法是在反相输入端使用一个额外的接地电容。在基于FDA的MFB滤波器设计中,为改善回路相位裕度,需要时可以在输入端跨接一个差分电容器,以便在LG = 0dB交叉处形成更高的噪声增益。

f0附近的最小LG与滤波器响应形状通过几种方式相互影响:

由于环路增益最低,这会是响应中的峰值增益误差频率;

这也会是整个响应范围内的最大闭环输出阻抗;

最小环路增益也意味着最小谐波失真抑制。

增益带宽调整程序通常包含运放Aol影响,但很少包含输出阻抗峰值。LG减小了特定器件的开环输出阻抗,但开环输出阻抗可能本身电抗非常大,直到最近才在现代轨到轨输出器件中良好地建模。

表4总结了4种不同工具给出的4种方案示例的噪声增益Qz、得到的较低噪声增益零点、NG峰值和最小环路增益。报告的峰值噪声增益是在20 * log(11V/V)=20.8dB的DC值上的增加。11V/V的DC噪声增益是假定,该反相式滤波器是由零欧姆电源所驱动。

表4:带NG峰值和LG最小值的NG Qz和较低NG零点频率总结

在可能的情况下,最好在其它约束条件内拉高较低的噪声增益零点,使其尽可能接近f0。IntersilRC解决方案已经这么做了,此时来自DC噪声增益(20.8dB、11V/V)的峰值降低了——比Filterpro解决方案低大约2.6dB。请注意,所有4种解决方案中的峰值NG都明显高于响应形状中的1dB目标峰值。较低的噪声增益零点控制该最大NG峰值,它对此峰值不太大的低通有源滤波器设计中的最小环路增益值和SNR影响最大。全部4种设计的最小环路增益都相对较低,这是所选的17MHz GBW器件使然。使用更高(高于此处所选17MHz)的GBW器件有几个理由:

响应形状的标称偏差离期望目标更低;

f0区域的最小LG更高;

更低的输出谐波失真;

更低的闭环输出阻抗——与响应形状的精度和精确驱动负载的能力相互影响。

从这里的最小GBW设计开始,使用更快的运放会直接影响最小LG。例如,使用150MHz的OPA300与17MHz的LMP7711,会使表4中的最小LG增加20log(150/17) = 18.9dB。面向时域的应用通常更接受较低的最小LG。在需要最低谐波失真的地方,应考虑采用速度更快且静态电流增加最小的器件。

表5总结了使用修改后的LMP7711模型的4个设计示例的性能。显然,RC方案的微小差异会导致最终标称性能显著不同。

表5:LMP7711运放选择结果汇总

评论和建议总结

本文详细评估了标称拟合精度和一些动态范围。所有4种工具都使用理想运放,获得了很好的标称拟合精度——选择E96步长电阻值时,标称拟合误差 < 0.6%。所有的响应形状都偏离了目标,包括一款真正的运放——因此不应期望得到符合目标的完美标称拟合。使用最小增益带宽放大器进行操作可以显著节省功耗,但应与GBW调整方法结合使用,以减少标称拟合误差。

较新的工具(ADI、Webench和Intersil)可将R值调整到符合运放固有输入噪声指标的范围。然而,区分积分噪声的主要机制是噪声增益零点的布局。Intersil工具可增加Qz并降低噪声增益峰值,其它3种工具如何对待此策略尚不清楚。

工具开发和设计建议:

考虑到本文提及的指标,在选择放大器时,注意平衡GBW裕量与功耗;

尽可能在测试之前验证运放模型,并在需要时做相应修改以提高结果的有效性;

利用GBW调整算法,将解决方案的适用空间扩展到低得多的速度/功率运放和/或提高标称拟合精度;

将RC解决方案偏向更高的噪声增益Qz,这将提高SNR并改善NG峰值区域内的LG;

对于每个二阶级,允许直接设置目标极点。这样,用某些功能更强大的第三方工具生成的设计就可在运放供应商工具中实现,从而更好地将RC解决方案与运放参数绑定;

在5%E24步长中留出2%的电容容差,在1%E96步长中留出0.5%的电阻容差。它们比全E48电容器系列或E192电阻步长值更容易获得;

扩展MFB方案以包含衰减阶段。与SKF拓扑结构不同的是,反相MFB设计非常适用于衰减器——在实现或公式中没有任何约束,用户可以自由选择采用VFA运放或精密全差分放大器(FDA),这点非常有用。

有源滤波器设计的下一步是选择RC容差,然后运行蒙特卡罗(MonteCarlo)程序来评估此处考虑的标称起点的响应扩展。需要注意的是,全2%E48系列C0G(或NPO)电容器并不容易得到,但价格稍高的5%E24系列中的2%容差电容器则库存充足。电阻通常选用1%E96值。但是,E96步长中0.5%容差电阻值比全E192系列值更容易获得。响应会围绕标称值显著扩展,从5%的电容和1%的电阻变为2%的电容和0.5%的电阻,并且只增加很少的BOM成本(包括占大头的运放成本)。

评论