隔行不隔山 PCB系统设计软件让设计飞起来

对系统开发展设计工程师而言,要能同时兼顾IC设计、封装与印刷电路板(PCB)系统层级的设计,相当困难,也需要花更多时间一一了解。这并不表示工程师能力不足,而是这三领域各有不同的专业知识--隔行如隔山--要能通盘了解并设计出初步的系统,可能得花上一段时间。

本文引用地址:http://www.eepw.com.cn/article/201807/384390.htm明导国际(Mentor Graphics)系统设计部业务开发经理David Wiens表示,IC设计、封装与PCB系统设计都有标准规范可依循,且业者都针对自己的“强项”推出设计工具,以方便设计者设计其系统。然而这样的设计工具由于只针对IC设计进行,因此PCB系统设计工程师在设计时,仍须针对IC、封装与PCB系统的接脚路径进行规划,而IC设计与封装领域对PCB系统设计工程师来说犹如一堵高墙,要让每个阶段的接脚路径设计都顺利完成,将旷日费时,产品上市时间将因而拉长。

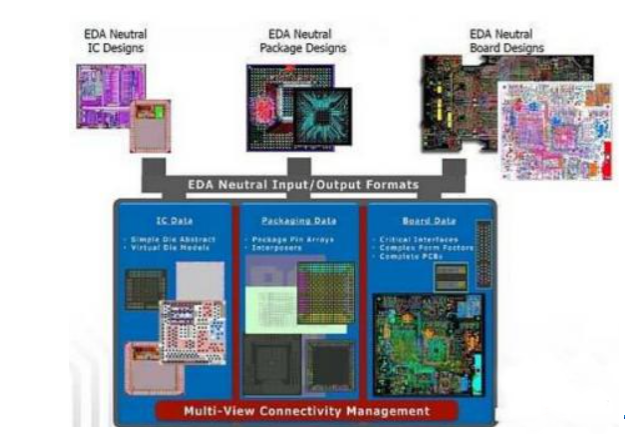

有鉴于此,明导国际发布Xpedition Package Integrator软体流程,协助PCB设计工程师顺利进行系统设计。Wiens指出,Xpedition Package Integrator可该解决方案可确保IC、封装和PCB三者间接脚路径的规划是相符的,且其精简设计工具可以让设计工程师在IC、封装与PCB的接脚位置、走线方式,都可快速且轻松的完成。

图1 采用虚拟晶片模型概念,实现IC到封装协同优化的PCB系统设计软体,可加快设计时程

换句话说,透过这种协同设计的方式,设计工程师只要在系统页面上,简单的画出各接脚间的走线方式,软体就可迅速将呈现正确的走线与接脚对应,工程师无须在一团混乱中,慢慢对应、找寻IC到封装、封装到PCB正确的接脚与走线。

如此一来,不仅可以让设计工程师快速优化互连路径,还可减少PCB所需的层数,进而降低封装基底和PCB成本。该设计软体能实现这样的便利性,是由于该软体整合各家IC设计、封装厂与PCB业者的产品相关资讯与档案格式。

更重要的是,解决了PCB设计工程师遭遇的难题之后,设计工程师将可加速系统设计时间。Wiens认为,就难度较低且简单的PCB系统设计为例,过去工程师平均得花两周时才能完成设计,而Xpedition Package Integrator软体流程可将设计时间缩短至5~10分钟。

评论