胡正明:技术创新可能让半导体晶体管密度再增加1000倍

“半导体市场正在经历由技术推动到需求推动的转变。而半导体技术上的创新,可能让半导体晶体管密度再增加1000倍,仍有巨大空间。”近日,美国加州大学伯克利分校教授、国际微电子学家胡正明在接受集微网采访时表示。

本文引用地址:http://www.eepw.com.cn/article/201805/380203.htm自1965年摩尔定律提出以来,历经半个多世纪的发展,如今越来越遭遇挑战,特别是新世纪以来,每隔十年,摩尔定律以及半导体的微型化似乎便会遭遇到可能终止的危机。

胡正明发明了鳍型晶体管(FinFET)以及「全耗尽型绝缘层上硅晶体管」(FD-SOI),两大革命性创新为半导体带来新契机。 2011年5月英特尔宣布使用FinFET技术,包括台积电、三星、苹果也都陆续采用FinFET,开创了摩尔定律被唱衰后的新契机。

目前,台积电宣布7纳米进入量产,预计在2019上半年展开5纳米制程风险试产,对于产业走到5纳米,胡正明表示,5纳米未必代表着极限。但要接受“物理极限”的客观存在,在以往的技术中,可以通过测量线宽的方式去直观的理解,但当工艺技术走进14nm、10nm、7nm,线宽已然成为了一个标签。

“因为真正的目的是要实现速度、性能增加和功耗、成本减少,所以推进半导体微型化不一定是要减少尺寸,比如存储器已经往三维方向演进。”胡正明说。

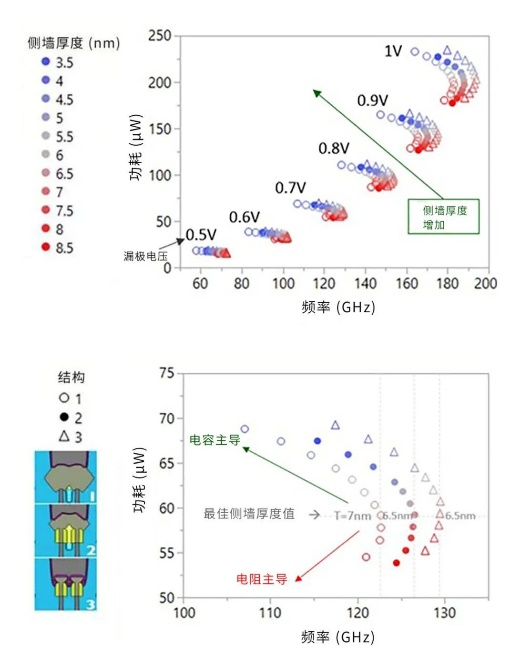

在降低功耗方面,胡正明表示,通过负电容晶体管设计的引进,会将CMOS的电压降低至0.4V、0.3V,甚至0.2V。因为负电容器件(铁电材料)的引进,在不同机制下可能会带来速度限制的问题,但胡正明教授指出,到目前为止,它的限制还不会高过半导体晶体管的速度。

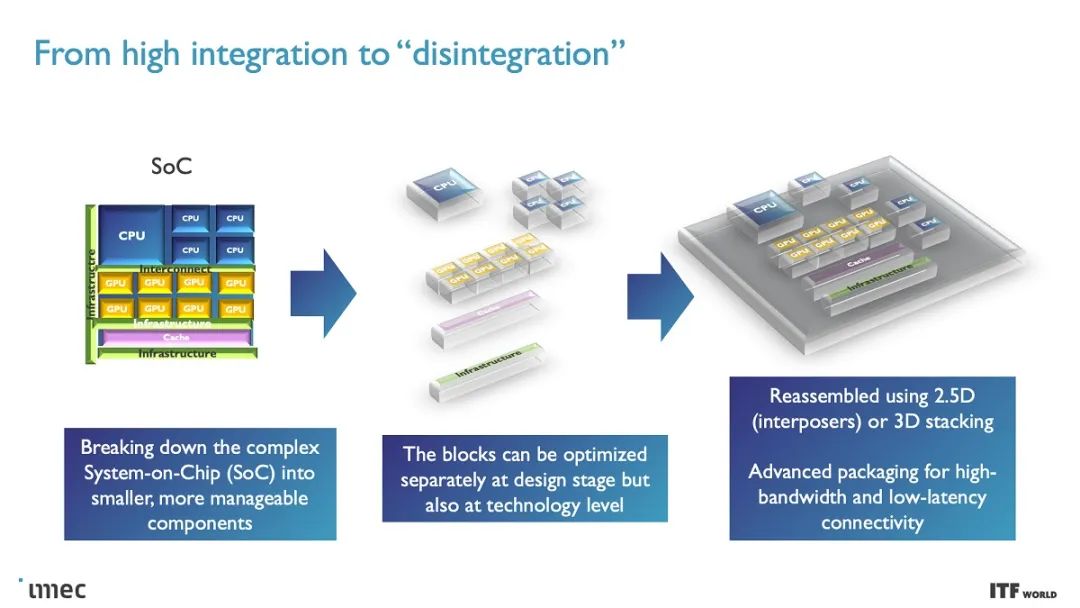

胡正明认为,正如同三维堆叠可以降低成本和增加密度,推动3D NAND闪存成为主流,堆叠的二维半导体电路也是较好的实现方式。

二维半导体只有2—3个原子的厚度,不需要人工打磨。而他与伯克利研究团队做的工作,首先是可以让二维的半导体长在垂直的鳍式晶体管的结构上,即二维半导体可以用来盖“高楼”;第二,可以让二维半导体长在大面积的晶圆上,让它覆盖了垂直薄膜的晶体管,同时可以在一片芯片上做两层、三层甚至更多层的电路;第三,用二维半导体制作的晶体管,可以把晶体管的三极缩小到1纳米的宽度。

在胡正明看来,半导体微型化的进程将会减慢,一方面因为原子的尺寸固定,会达到物理极限;另一方面,光刻和其他制造技术变得越来越昂贵。但创新永远是行业的主题,通过创新技术,逐渐引入新材料,对于成本、功耗和性能将会持续改善。

评论