14张图看懂半导体工艺演进对DRAM、逻辑器件、NAND的影响

编者按:DRAM工艺尺寸的缩减正在面临基本的物理限制,目前还有没有明确的解决方案,由于印刷需求的推动,DRAM的清洗复杂度也在增加。

3D NAND取代了2D NAND,成为NAND产品的技术选择,现在3D NAND的比特出货量也已经超过了2D NAND。3D NAND尺寸的缩减是由层数进行表征的,驱动力来自于层沉积和蚀刻取代了2D NAND中的光刻工艺。

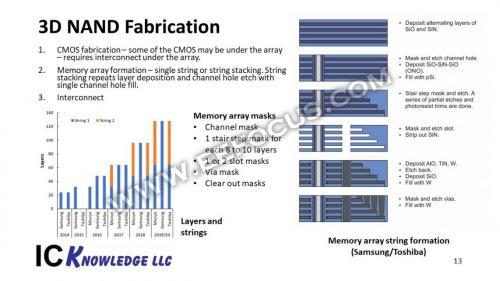

在第13张幻灯片中,我展示了3D NAND的三个主要制造步骤-CMOS制造、存储阵列制造和互联。三星和东芝(NAND产品的头两号供应商)使用的基本存储阵列工艺如右侧图所示。随着层数的增加,存储器阵列必须在“位串堆叠”阶段拆分成多个段。左下图显示了三家领先供应商的层数和位串。

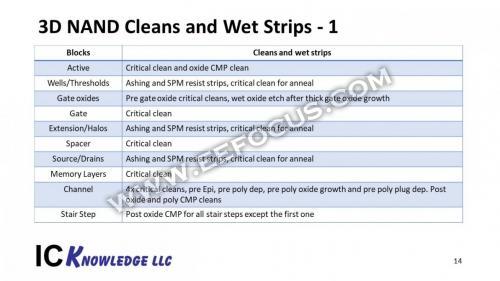

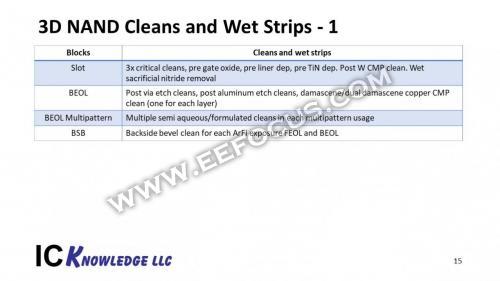

在第14张和第15张幻灯片中,我介绍了一些主要的3D NAND工艺模块,并讨论了这些模块对清洗和湿条带的需求。

幻灯片16展示了3D NAND的总清洗次数与三星3D NAND工艺的层数。3D NAND清洗次数之所以随着层数增加而增加,主要是因为阶梯成型时的CMP清洗。在第一阶梯掩模之后,每个后续掩模都需要在施加掩膜之前通过CMP清洗将层平坦化。

结论

DRAM工艺尺寸的缩减正在面临基本的物理限制,目前还有没有明确的解决方案,由于印刷需求的推动,DRAM的清洗复杂度也在增加。

随着行业向5nm和3nm的推进,逻辑器件的工艺尺寸将持续缩减。纳米线和纳米片将对清洗带来新的挑战。随着掩膜数量的则更加,以及多重图案化方案越来越复杂,逻辑器件的清洗次数也在增长。

NAND工艺尺寸的缩减已经完成落脚到了3D NAND层数的增加上。由于阶梯成型需要CMP清洗,3D NAND器件的清洗次数也在不断增加。

评论