一种基于40nm CMOS工艺的新型温度补偿、高电源抑制比的带隙基准源

作者 / 徐成阳 电子科技大学 微电子与固体电子学院(四川 成都 610054)

本文引用地址:http://www.eepw.com.cn/article/201803/377634.htm徐成阳(1993-),男,硕士生,研究方向:SOC/SIP 系统芯片技术。

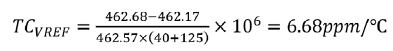

摘要:基于TSMC40LP工艺设计了一种新颖的温度补偿、高电源抑制比的带隙基准源。本设计采用全MOSFET设计,工作于1.1 V电源电压,通过将MOSFET偏置在零温度系数工作点,并结合温度补偿技术和有源衰减电路,实现在-40 ℃~125 ℃内温度变化系数为6.6 ppm/℃,低频下电源抑制比为93 dB,高频下电源抑制比为56 dB,与此同时,利用阻抗调试对环路稳定性进行了补偿。

0 引言

随着集成电路产业的飞速发展,特别是在高精度集成电路的设计中,带隙基准源都是一个非常重要的模块,该模块可以为其他电路提供高精度的基准源,在理想情况下,带隙基准源的输出电压与电源电压变化、工艺参数变化以及温度变化等都无关。通过将具有不同温度系数的电压按一定系数相叠加,降低输出电压的温度系数是带隙基准源的基本原理。为了进一步降低带隙基准源的输出电压温度系数,一般需要进行一阶曲率补偿,削弱温度对输出电压精度的影响,得到的基准源输出电压温度系数通常也在20 ppm/℃左右,若想得到更高精度的基准输出电压,则需要进行更为复杂的高阶温度项补偿,虽然可以达到10 ppm/℃左右温度系数的效果[1],但是增加了设计复杂度,难以实现。

全MOSFET电压基准几乎是低电源电压应用下的唯一选择,近年来,基于低电源电压下的设计都是依赖于MOSFET工作于亚阈值的特性,使得MOSFET工作的温度特性类似于BJT,从而可以达到低功耗的要求,然而由于结漏电会影响亚阈值特性,使得MOSFET的亚阈值特性只在有限的温度范围内可靠,所以通常要达到宽的温度操作范围以及低的温度系数都伴随着大的功耗[2]。

1 电路介绍

本次设计利用MOSFET超阈值区的零温系数工作点,通过合理偏置MOSFET的零温系数工作点,并结合温度曲线补偿技术,在-40 ℃~125 ℃范围内达到低的温度系数为6.6 ppm/℃,并且通过采用有源衰减器以及阻抗调试补偿,得到较高的基准输出电压的电源抑制比,低频下达到93 dB,高频下达到56 dB。

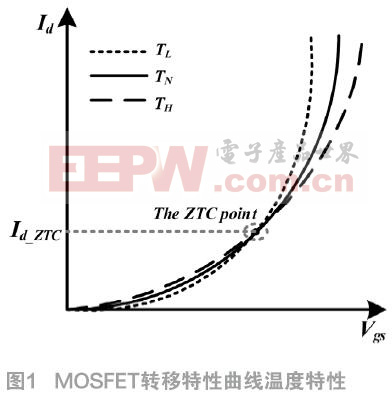

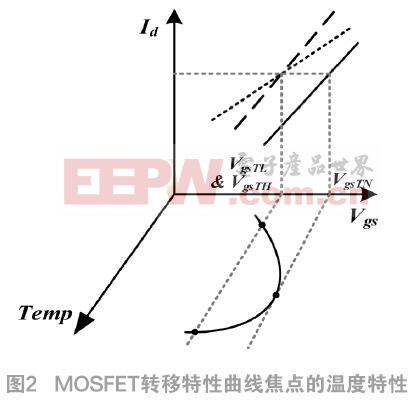

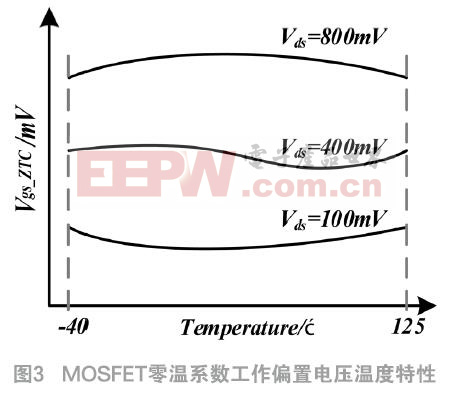

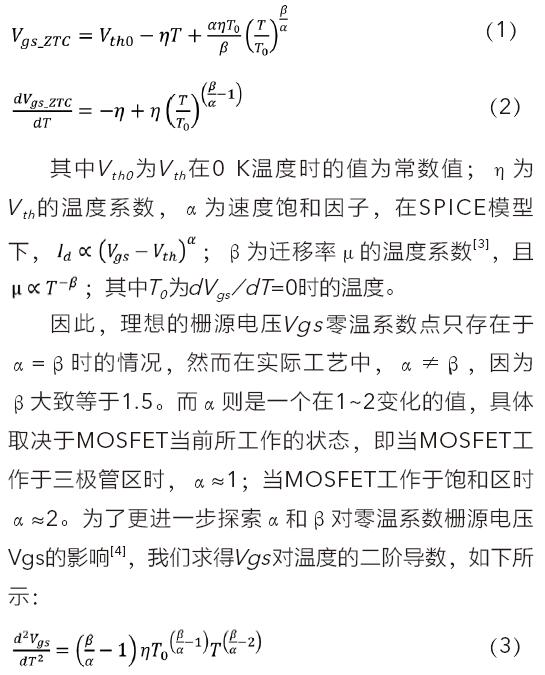

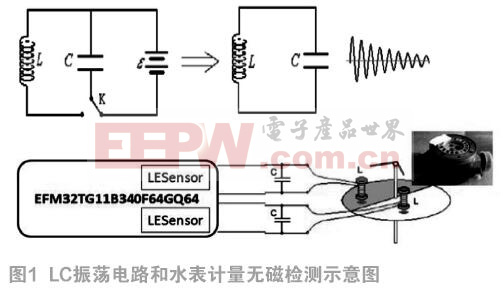

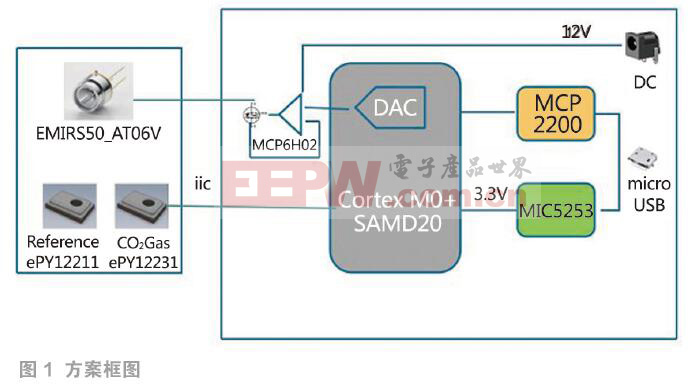

MOSFET零温系数点主要受阈值电压和迁移率的影响,图1显示了MOSFET的转移特性中漏源电流(Id)随栅源电压(Vgs)在不同温度(TL、TN、TH)下的变化曲线。然而实际上MOSFET的转移特性曲线不会理想地相较于某一点,而是成为一系列相交点簇,焦点的位置有较为敏感的温度特性,主要取决于Vgs对于温度的特性[3]。而零温系数工作点的漂移主要源自于在载流子迁移率温度系数和速度饱和指数不匹配所造成的二阶效应。根据基础SPICE-MOS模型[4]可得:

这是因为MOSFET的阈值电压Vth具有负温系数,在低温时,Vth较大,使得Vds>Vgs-Vth,MOSFET工作于饱和区;而当在高温时,Vth较小,使得Vds<Vgs-Vth,MOSFET工作于三极管区。这样就可以利用合理的偏置漏源电压Vds在全温度范围内对温度的二阶效应进行补偿,使得Vgs_ZTC具有最小的温度系数。

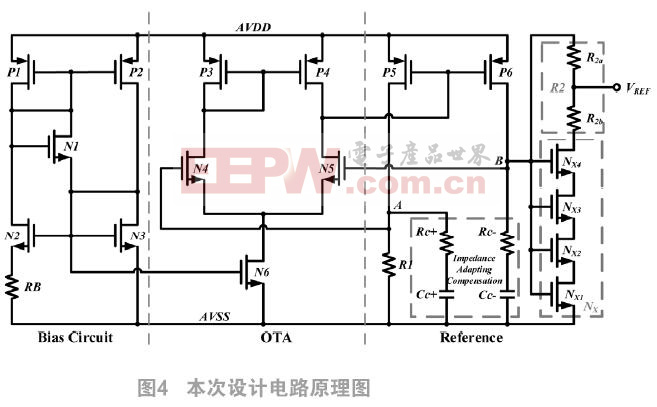

如图4所示为本设计基准电压电路图,其中偏置电路由P1-2、N1-3和RB组成;运算放大器由P3-4和N4-6构成;基准产生电路由P5-6、R1、R2以及NX构成。其中Rc与Cc为两支环路的阻抗补偿电路,通过提供一个左半平面的零点抵消环路主极点的影响,以对两支环路(正反馈环路与负反馈环路)的稳定性进行补偿[7],避免了传统的密勒补偿带来的极点推移,导致主极点推移向原点方向从而降低了高频下输出基准电压的PSRR特性。

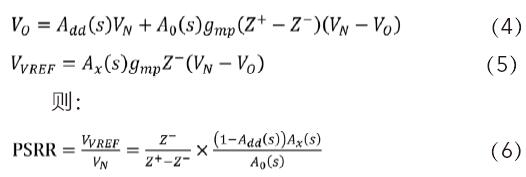

与此同时,在输出基准电压的PSRR方面,本设计利用有源衰减器,提升了高频下输出基准电压的PSRR特性。如图虚线中所示,类似于电流源[5],由此可以推算其PSRR如下:

其中,VN为电源噪声,VO为运算放大器小信号输出电压,Add(s)为电源噪声到运放输出的增益,在较宽的频率范围内其大致都为一个常数[6],Ax(s)为有源衰减器的增益,Z+与Z-分别为运算放大器正负输入端的阻抗,而A0 (s)=A0 ⁄ (1+s ⁄ωp0 ) ,A0(s)为运算放大器的增益,ωp0为运算放大器的输出极点,在高频时的PSRR的衰减主要是由于极点ωp0造成的,而Ax(s)=1-gm_NxR2a ,则可以设置R2a≈1⁄gm_Nx,使得衰减器的增益在接近ωp0处约为0 ,则基准输出电压的PSRR在高频下能够得到大的改善[6]。

2 设计与仿真

本次设计基于TSMC 40 nmLP工艺制程,设计电路图中各个MOSFET尺寸如表1所示。

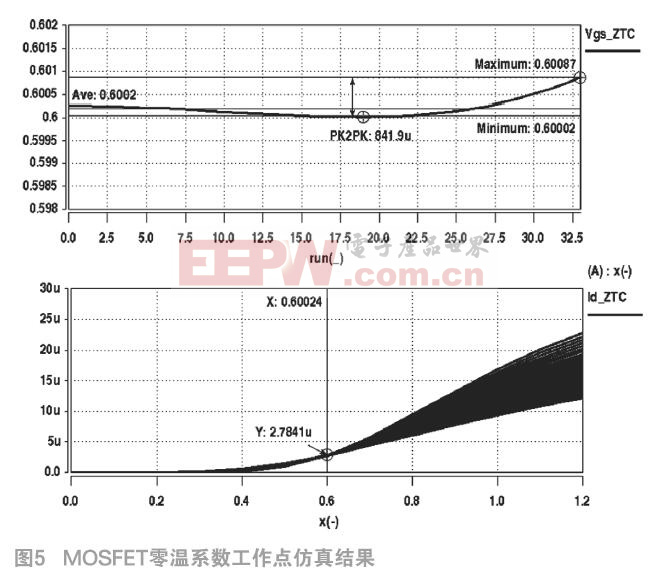

为达到较为准确的零温系数偏置点,首先需要将NX偏置在零温系数栅源电压处,则可通过调节电阻R1,R1=Vgs_ZTC ⁄ Id_ZTC,利用运算放大器虚短虚短特性,一级电流镜的作用,使得B点电压钳位等于A点电压且两条支路电流相等,即可使得MOSFET偏置于零温系数栅源电压点;其中MOSFET的零温系数栅源电压及漏源电流需要通过实际的仿真得到,具体仿真结果如图5所示。

如图5所示,最佳零温系数偏置点的Id_ZTC≈2.784 μA,Vgs_ZTC≈600.2 mV。

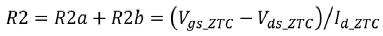

再者,通过调节电阻R2a以及R2b来调节NX的漏源偏置电压以优化零温系数工作点进一步减小温度敏感度,使得Vgs_ZTC随温度变化曲线在低温段具有最大值,而在高温段具有最小值,实现全温度范围内的二阶补偿,此时最优的漏源工作电压为Vds_ZTC,则:

通过仿真得到的最佳Vgs_ZTC随温度变化曲线如图5所示,在全温度范围内变化幅度为841.9μV,此时的Vds_ZTC≈300 mV。

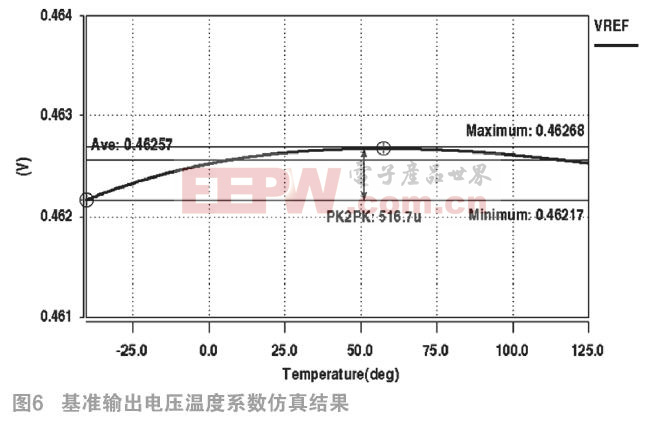

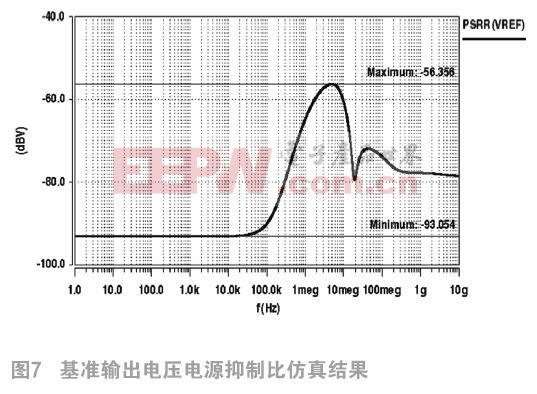

最终电路仿真得到输出基准电压随温度变化曲线如图6所示。由图6可知,得到的输出基准电压的温度系数为:

(7)

(7)

对于输出基准电压PSRR特性,仿真结果如图7所示。由图7仿真结果可知,低频下输出基准电压低频下的PSRR为93 dB,最小为56 dB,而高频下输出基准电压PSRR在60 dB以上。

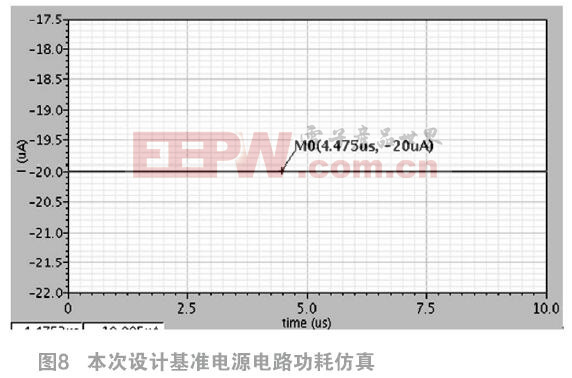

本次设计基准电压电路总功耗仿真如图8所示。由图8仿真结果可知,在低压1.1 V电源电压下,基准电压电路总功耗为22 μW。

3 结论

本次设计利用MOSFET栅源电压零温系数点温度特性,并采用一种新颖的基准电压曲率补偿技术与有源衰减器,在基于TSMC 40 nmLP工艺制程下,完成了一种工作于低压1.1 V的全MOSFET基准电压源。电源电压为1.1 V,输出基准电压VREF=462 mV,典型下在-40 ℃~125 ℃的温度系数TC为6.68 ppm/℃,低频下的PSRR达到93 dB,最小为56 dB,而高频下(>10MHz)PSRR均在60 dB以上,基准电压电路总功耗为22 μW。

参考文献:

[1]L. Guo, T. Ge, and J. S.Chang, “A 101 dB PSRR, 0.0027% THD+N and 94% power-efficiency filterless class D amplifier,” IEEE J. Solid-State Circuits, vol. 49, no. 11, pp. 2608-2617, Nov. 2014.

[2]P. K. T. Mok and K. N. Leung, “Design considerations of recent advanced low-voltage low-temperature-coefficient CMOS bandgap voltage reference,” in Proc. Custom Integr. Circuits Conf., Oct. 2004, pp. 635-642.

[3]I. M. Filanovsky and A. Allam, “Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits,” IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 48, No. 7, pp. 876-884, Jul. 2001.

[4]K. A. Bowman, B. L. Austin, J. C. Eble, X. Tang, and J. D. Meindl, “A physical alpha-power law MOSFET model,” IEEE J. Solid-State Circuits, vol. 34, No. 10, pp. 1410-1414, Oct. 1999.

[5]D. V. Kerns, “Optimization of the peaking current source,” IEEE J. Solid-State Circuits, vol. 21, No. 4, pp. 587-590, Aug.1986.

[6]M. S. J. Steyaert and W. Sansen, “Power supply rejection ration in operational transconductance amplifiers,” IEEE Trans. Circuits Syst., vol. 37, No. 9, pp. 1077-1084, Sep. 1990.

[7]X. Peng, W. Sansen, L. Hou, J. Wang, and W. Wu, “Impedance adapting compensation for low-power multistage amplifiers,” IEEE J. Solid-State Circuits, vol. 46, No. 2, pp. 445-451, Feb. 2011.

[8]A. Shrivastava, K. Craig, N. E. Roberts, D. D. Wentzloff, and B. H. Calhoun, “A 32nW bandgap reference voltage operational from 0.5V supply for ultra-low power systems,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2015, pp. 1-3.

[9]L. Magnelli, F. Crupi, P. Corsonello, C. Pace, and G. Iannaccone, “A 2.6nW, 0.45V temperature-compensated subthreshold CMOS voltage reference,” IEEE J. Solid-State Circuits, vol. 46, No. 2, pp. 465-474, Feb. 2011.

[10]X. L. Tan, P. K. Chan, and U. Dasgupta, “A sub-1-V 65nm MOS threshold monitoring-based voltage reference,” IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, No. 10, pp. 2317-2321, Oct. 2015.

本文来源于《电子产品世界》2018年第4期第52页,欢迎您写论文时引用,并注明出处。

评论